인프런 커뮤니티 질문&답변

Artwork 50ohm 매칭 관련 질문

해결된 질문

작성

·

95

0

안녕하세요 삼코치님, Artwork 진행 중인데 궁금한 점이 생겨서 질문 남깁니다.

PHY칩과 Main contoller의 RX/TX 통신선로 50ohm 매칭을 진행하고 있습니다.(25MHz 통신으로 10/파장 = 0.4mm보다는 길어져서 반드시 매칭이 필요하다고 생각했습니다.)

Kicad에서 제공하고 있는 calculator tool로 50옴 매칭을 계산한 결과(현 보드셋업 반영: dielectric, dielectric thickness 등등 ) width가 0.9mm로 산출되었습니다.

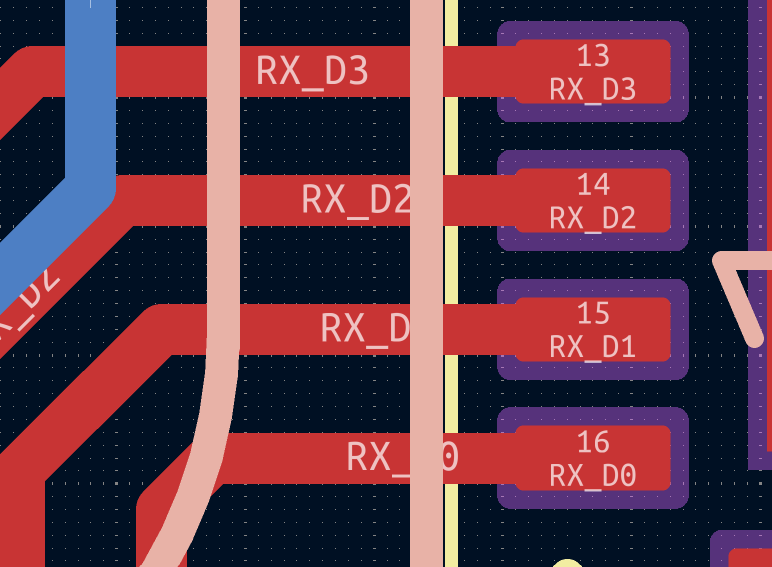

해당 width는 인접 핀에서 신호선을 가져오기에 너무 커서 routing이 어려운 상황입니다.(0.3mm가 각 핀에서 보여지는 width입니다.)

이런 문제를 해결하기 위해 저는 아래와 같은 방법을 확인해봤습니다.

1. 일부 bit선은 via를 통해 bottom plate에서 routing 진행: 각 데이터별 신호선의 길이를 맞추는 장점은 있지만, via로 인한 discontinuity 발생

2. 보드 셋업 변경: pcb dielectric 두께를 0.48mm에서 더 얇게 변경(제조사 마다 다르기 때문에 맞는 업체를 찾는 게 가능할지 미지수)

제가 생각한 방법 외에 다른 방도가 있는지, 아니면 제가 놓치고 있는 개념이나 포인트들이 있는지 확인해주시면 감사하겠습니다. 또한 어떤 방법이 더 현실적인 방안인지 알고 싶습니다.

감사합니다.

답변 1

0

안녕하세요, 답변 남겨드립니다.

현재 RX_D0~D3 신호선은 핀 간 피치가 매우 좁은 상태에서 병렬로 라우팅되어 있으며, 각각의 선폭은 약 0.3mm 수준으로 제한되어 있는 것으로 보입니다. 이는 Kicad 계산 툴을 기준으로 한 50Ω 임피던스 매칭 요구 조건인 약 0.9mm 선폭과 비교했을 때 명백한 불일치가 발생하며, 현 구조에서는 해당 선폭을 확보하는 것이 물리적으로 불가능한 상황입니다. 이러한 제약은 특히 디지털 병렬 신호선(RX 데이터 버스)처럼 여러 신호가 동시에 스위칭되는 경우에 더욱 문제가 될 수 있는데, 이는 단순한 선폭 문제를 넘어서 crosstalk과 신호 무결성(SI) 이슈로 이어질 수 있습니다.

가장 먼저 짚고 넘어가야 할 부분은, 해당 신호들이 25MHz 대역이라는 점만으로는 반드시 임피던스 매칭이 필요하다고 단정할 수 없다는 것입니다. 일반적으로 임피던스 매칭은 파장 대비 선로 길이가 1/10 이상일 때부터 고려해야 하지만, 실제로는 rise time이 수 ns 미만으로 짧은 경우에는 주파수와 관계없이 고속 신호로 취급하게 됩니다. 즉, PHY 칩이 출력하는 신호의 edge rate가 빠를 경우, 25MHz 신호라 하더라도 임피던스 매칭은 필요한 조건일 수 있습니다.

현재와 같이 선폭이 제한된 상황에서는 전통적인 microstrip 구조만으로는 50Ω 구현이 거의 불가능하며, 다른 구조적 접근이 필요합니다. 첫 번째로 고려할 수 있는 방법은 coplanar waveguide with ground (CPWG) 구조입니다. 이는 신호선 양옆에 GND 라인을 배치하여 전자기장을 집중시키는 방식으로, 동일한 dielectric 두께에서 더 좁은 선폭으로도 50Ω 근사값을 구현할 수 있습니다. 예를 들어, 0.3mm 선폭에서도 양옆의 GND spacing을 적절히 설정하면 CPWG 기준으로는 50Ω에 가깝게 설계할 수 있으며, 이는 Kicad의 CPWG 계산 모드로 확인 가능합니다.

두 번째 방법은 stack-up 구조 자체를 수정하는 것입니다. 즉, GND layer를 더 가까운 위치에 두거나 dielectric 두께를 줄이는 방향으로 조정하는 것입니다. 예를 들어, 일반적인 4-layer FR4 보드에서 dielectric 두께를 0.48mm에서 0.20.25mm 수준으로 줄이면, 선폭 0.30.4mm에서도 50Ω 달성이 가능해집니다. 다만 이 경우에는 제조사와의 협의가 필요하며, 양산성이나 단가 측면에서 고려해야 할 요소들이 많습니다.

세 번째로 고려할 수 있는 방법은 일부 라인을 bottom layer로 내려 routing을 분산하는 것입니다. 현재처럼 4개 병렬선을 동시에 라우팅해야 할 경우, 위상차가 발생하지 않도록 length matching이 필요하므로 via를 사용할 때는 반드시 적절한 보정 및 GND stitching이 동반되어야 합니다. 물론 via를 통한 layer 변경은 고속 신호에서 signal discontinuity를 유발할 수 있지만, 25MHz 정도의 relatively low-speed 기준에서는 충분히 허용 가능한 수준입니다.

또한, 단일 선로의 임피던스뿐 아니라 송수신단의 임피던스 조건 역시 고려되어야 합니다. 실제로 송신단의 output impedance와 수신단의 input impedance가 50Ω에 가까운 값으로 설계되어 있다면, PCB 선로가 약간의 mismatch를 가지더라도 시스템 전체에서의 reflection은 허용 가능한 수준일 수 있습니다. 따라서 반드시 trace만을 기준으로 50Ω을 달성해야 한다는 강박에서 벗어나, 시스템 레벨에서의 신호 무결성을 보는 것이 보다 실용적이고 현실적인 접근이 됩니다.

결론적으로, 현재와 같은 물리적 제약을 가진 환경에서는 microstrip만을 고려한 설계는 불가능에 가깝고, CPWG 또는 stack-up 조정이 필수적인 조건이 됩니다. 제조 공정의 현실성과 신호 integrity 사이의 절충점을 찾아야 하며, 특히 이와 같은 좁은 routing 공간에서는 주변 GND와의 상대 배치를 통해 EM field를 통제하는 방식의 접근이 설계 효율성과 신뢰성을 동시에 확보할 수 있는 길입니다. 설계 의도와 시스템 조건에 따라 판단하되, 만약 CPWG 방식 적용과 stack-up 협의가 가능하다면, 0.3mm 선폭에서도 충분한 매칭 성능을 확보할 수 있을 것입니다.