인프런 커뮤니티 질문&답변

CMOSP 소자 단자에 대해서

작성

·

107

0

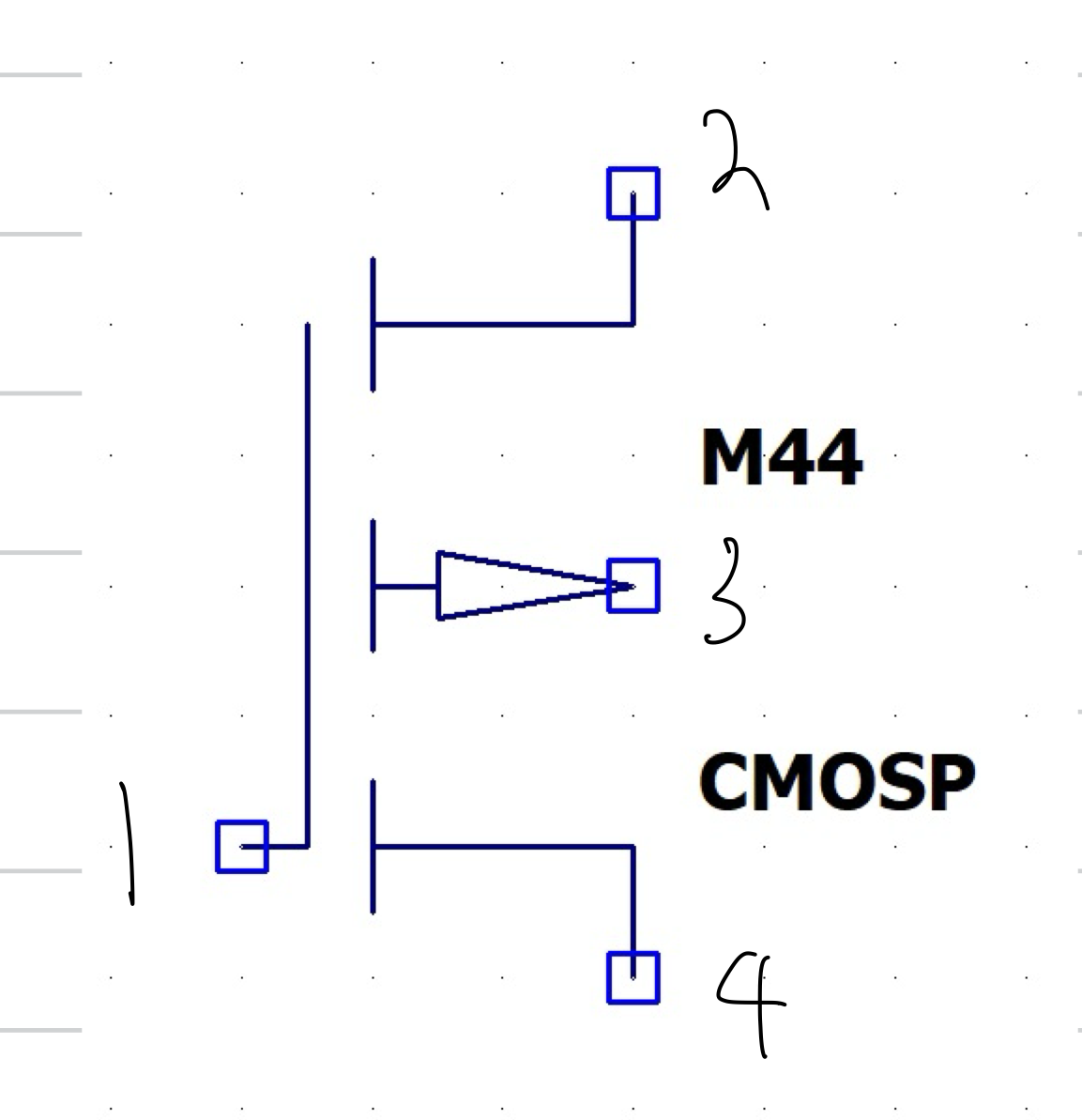

안녕하세요 삼코치님, 1,2,3,4번 단자가 정확히 어떤건지 좀 헷갈려서 질문드립니다 감사합니다!

퀴즈

아날로그 회로에서 Bandgap Reference (BGR)의 주된 역할은?

전압 강하를 줄여 전력 효율을 높인다.

온도와 공급 전압 변동에도 일정한 기준 전압을 제공한다.

디지털 신호의 전압 레벨을 변환한다.

고주파 클럭 신호를 생성한다.

답변 1

0

안녕하세요, 답변 남겨드립니다.

1번 단자는 게이트(Gate)입니다. 회로 상에서 삼각형 형태의 논리 입력 신호선과 직접 연결되어 있고, 이는 트랜지스터의 문턱 전압 이상에서 스위칭을 제어하는 전압 제어 입력 단자입니다. PMOS의 특성상, 게이트 전압이 소스보다 낮을 때 턴온되므로, 이 단자는 반드시 신호 제어선과 연결되어야 하며, 실제 도면에서도 해당 조건을 충족하고 있습니다.

2번과 4번 단자는 소스(Source)와 드레인(Drain)입니다. PMOS는 기본적으로 소스에서 드레인으로 정공이 흐르지만, 물리적으로 대칭 구조이기 때문에 이 두 단자는 기능적으로는 교환 가능합니다. 즉, 연결된 회로 전위에 따라 자동으로 소스와 드레인이 결정되며, 공정상 또는 시뮬레이션 상에서도 전류의 흐름과 상위 회로 조건에 따라 소자 내부에서 적절히 해석됩니다. 따라서 이 두 단자는 드레인/소스 쌍으로 간주됩니다.

3번 단자는 벌크(Bulk)입니다. PMOS 트랜지스터는 N-well 위에 형성되며, 이 벌크 단자는 반드시 N-well 바이어스를 위해 소스 전위(VDD)에 연결되어야 합니다. 벌크는 트랜지스터의 본질적 동작에는 직접 관여하지 않지만, 기생 다이오드 전류, 바디 이펙트, latch-up 방지 등 회로 안정성 확보를 위한 핵심 단자입니다. 이 단자를 잘못 연결하거나 floating 상태로 두면, 실리콘 내부에서 원하지 않는 전류 경로가 형성되어 소자 신뢰성이 크게 저하될 수 있습니다. 따라서, 반드시 source와 동일 전위로 연결하는 것이 기본 설계 원칙이며, 주어진 회로에서도 해당 단자는 source 전위와 함께 N-well 전위로 명확하게 정의되어야 합니다.

결론적으로, 1번은 게이트, 2번과 4번은 드레인과 소스로서 대칭 구조, 3번은 벌크입니다. 이는 단지 가능성의 문제가 아니라, 소자 구조상 반드시 그래야만 하는 물리적 필수 조건입니다. PMOS는 N-well 공정에서 동작하기 때문에, bulk가 반드시 VDD에 연결되어야 하며, 이때 소스 전위와 동일하게 두는 것이 latch-up을 방지하는 가장 기본적인 공정 규칙입니다. 이러한 전제는 모든 CMOS 회로 설계, 특히 Layout Versus Schematic(LVS), Design Rule Check(DRC), 그리고 공정 일치성(Process Compatibility)을 전제로 한 설계에서 절대적인 기준입니다. 바뀔 수 있습니다. PMOS는 대칭 구조를 가지며, 전류는 일반적으로 소스에서 드레인 방향으로 흐르지만, 소스와 드레인은 회로상 연결된 전위 차에 따라 기능이 결정됩니다. 예를 들어, 한쪽이 VDD에 가까운 높은 전위에 연결되고, 다른 쪽이 출력 노드에 연결되어 낮은 전위를 갖는다면, 높은 전위를 가진 쪽이 소스로, 낮은 전위를 가진 쪽이 드레인으로 동작하게 됩니다. 이처럼 2번과 4번은 구조적으로는 대칭이며, 전위 조건에 따라 상대적인 소스/드레인 역할이 동적으로 결정되는 셀입니다.

가장 주의 깊게 보아야 할 부분은 3번 단자인데, 이는 트랜지스터의 벌크(Bulk), 혹은 바디(Body) 단자로 해석하는 것이 타당합니다. PMOS는 CMOS 공정 상 N-well 위에 형성되며, 이 때 벌크는 반드시 N-well에 연결되어야 합니다. 일반적으로는 소스와 bulk를 동일 전위(VDD)로 연결하여, 기생 다이오드가 순방향으로 턴온되지 않도록 하고 latch-up을 방지하는 것이 기본 설계 원칙입니다. 하지만 특정 회로에서는 bulk를 독립적으로 바이어스 하거나, 제어 가능한 노드로 분리해두는 경우도 있으며, 이는 고급 전력 제어 회로나 body effect를 이용한 설계 등에서 발생할 수 있습니다. 주어진 회로에서 3번 단자가 인버터와 무관하게 독립적으로 표현되어 있는 점을 고려하면, 이 단자는 설계자가 직접 제어하거나, N-well 바이어스를 따로 연결해줄 목적으로 분리된 bulk 단자일 가능성이 높습니다.

요약하면, 이 CMOSP 셀에서 1번은 게이트로서 입력 제어 신호가 인가되는 단자이며, 2번과 4번은 회로 조건에 따라 상호 대칭적으로 소스 혹은 드레인의 역할을 할 수 있는 전류 경로이고, 3번은 소자의 전기적 안정성과 기생 동작 방지를 위해 반드시 제어되어야 하는 벌크 단자입니다. 이러한 구조는 CMOS 공정의 기본 전제인 NMOS와 PMOS의 상보적 관계와, N-well/P-substrate에 기반한 소자 배치 규칙에 근거하여 설계된 것으로, 아날로그·디지털 회로 설계 모두에서 매우 기본이 되면서도 중요한 해석 포인트입니다.

amp gain개선하려는 시도 하고있었는데, 답변이 큰 도움이 될듯합니다 감사합니다~~