인프런 커뮤니티 질문&답변

안녕하세요. 디버거 실습 강의 중 궁금한점이 생겨 질문드립니다.

해결된 질문

작성

·

83

0

안녕하세요. 디버거 실습 강의 중 궁금한점이 생겨 질문드립니다.

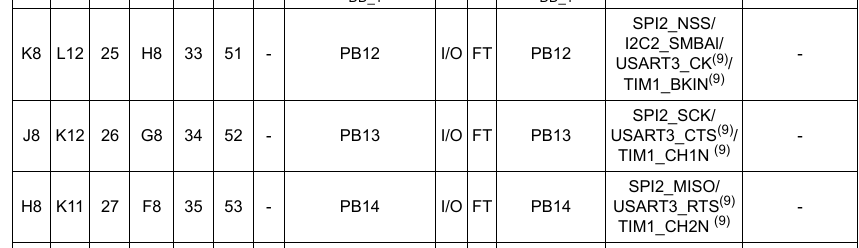

Port 라우팅을 진행할때, 각 포트들이 데이터 시트의 PIN Configuration 기준으로 포트 연결을 한다고 하셨습니다.

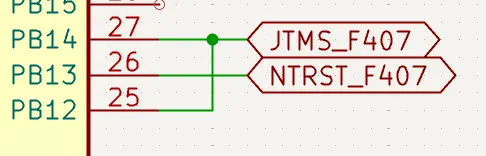

JTAG/SWD는 PIN Configuration에 나온대로 연결된 것으로 보이는데, 하기 이미지와 같이 메인 컨트롤러 F407과 연결되는 포트들은 PB12~14로 지정하셨던데, 데이터 시트에는 관련된 내용이 보이지 않아서요.

그냥 I/O Port 아무거나 사용해도 무방해서 아무 Port나 F407과 통신하는 포트로 지정하여 연결하신 걸까요?

아니라면 PB12, 14는 F407과 디버거 간의 JTAG 연결, PB13은 F407 리셋 포트로 지정하신 이유가 궁금합니다.

답변 1

0

안녕하세요, 답변 남겨드립니다.

PB12~PB14는 STM32F103의 일반적인 GPIO 포트이며, 해당 핀들이 특별히 하드웨어적으로 JTAG 기능이 고정된 것은 아닙니다. 이 경우 디버거는 내부적으로 소프트웨어를 통해 JTAG 신호를 생성하는 방식, 즉 비트뱅잉(bit-banging) 기법을 사용하게 됩니다. 비트뱅잉 방식은 MCU의 임의의 GPIO 핀을 활용하여 사용자가 정의한 논리 타이밍에 따라 JTAG 프로토콜을 모사하는 방식으로, 하드웨어 디버깅 프로토콜을 직접 구동하는 기법 중 하나입니다.

이와 같은 접근은 특히 ST-Link 호환 디버거나, Black Magic Probe와 같은 오픈소스 디버거 펌웨어에서 일반적으로 채택되는 방식입니다. 해당 프로젝트들은 STM32F103과 같은 저가형 MCU를 활용하여 소프트웨어적으로 SWD 또는 JTAG 인터페이스를 구현하고 있으며, 이 과정에서 특정 하드웨어 전용 핀을 사용하지 않고도 원하는 기능을 수행할 수 있습니다.

PB12는 JTMS 역할, PB14는 TCK 역할, PB13은 nTRST 또는 타겟 리셋 제어 역할로 사용되며, 이는 디버거 펌웨어 내에서 정의된 입출력 매핑에 따라 기능이 부여된 것입니다. 다시 말해, 물리적인 핀 기능보다는 디버거 소프트웨어가 해당 핀에 어떤 신호를 할당하느냐에 따라 의미가 결정됩니다. 이는 소프트웨어 기반 디버깅 장치에서는 매우 일반적인 설계 방식입니다.

따라서, 해당 핀들을 선택한 이유는 하드웨어적으로 고정된 기능 때문이 아니라, 디버거 MCU의 자유로운 GPIO 핀을 기반으로 필요한 JTAG 신호를 소프트웨어적으로 생성할 수 있기 때문입니다. 결과적으로, 사용된 PB12~PB14는 디버거 펌웨어에서 정의한 논리적 역할에 따라 배치된 것이며, 회로도나 데이터시트 상에 JTAG 전용 기능이 명시되지 않았더라도 기능상 문제가 발생하지 않습니다.

이와 같은 구조는 범용성 있는 디버거 설계를 가능하게 하며, 펌웨어 수정만으로도 다양한 핀 배치 및 타겟 MCU와의 연결 구성을 유연하게 변경할 수 있다는 장점이 있습니다.