Unbalancing latency can make deadlock부분 질문입니다

168

작성한 질문수 3

안녕하세요 🙂

맛비님

좋은 강의보면서 저의 개인적인 궁금증을 잘 풀어가고 있습니다.

질문이 하나 있습니다.

HDL 25장 10분쯤 나오는 내용입니다.

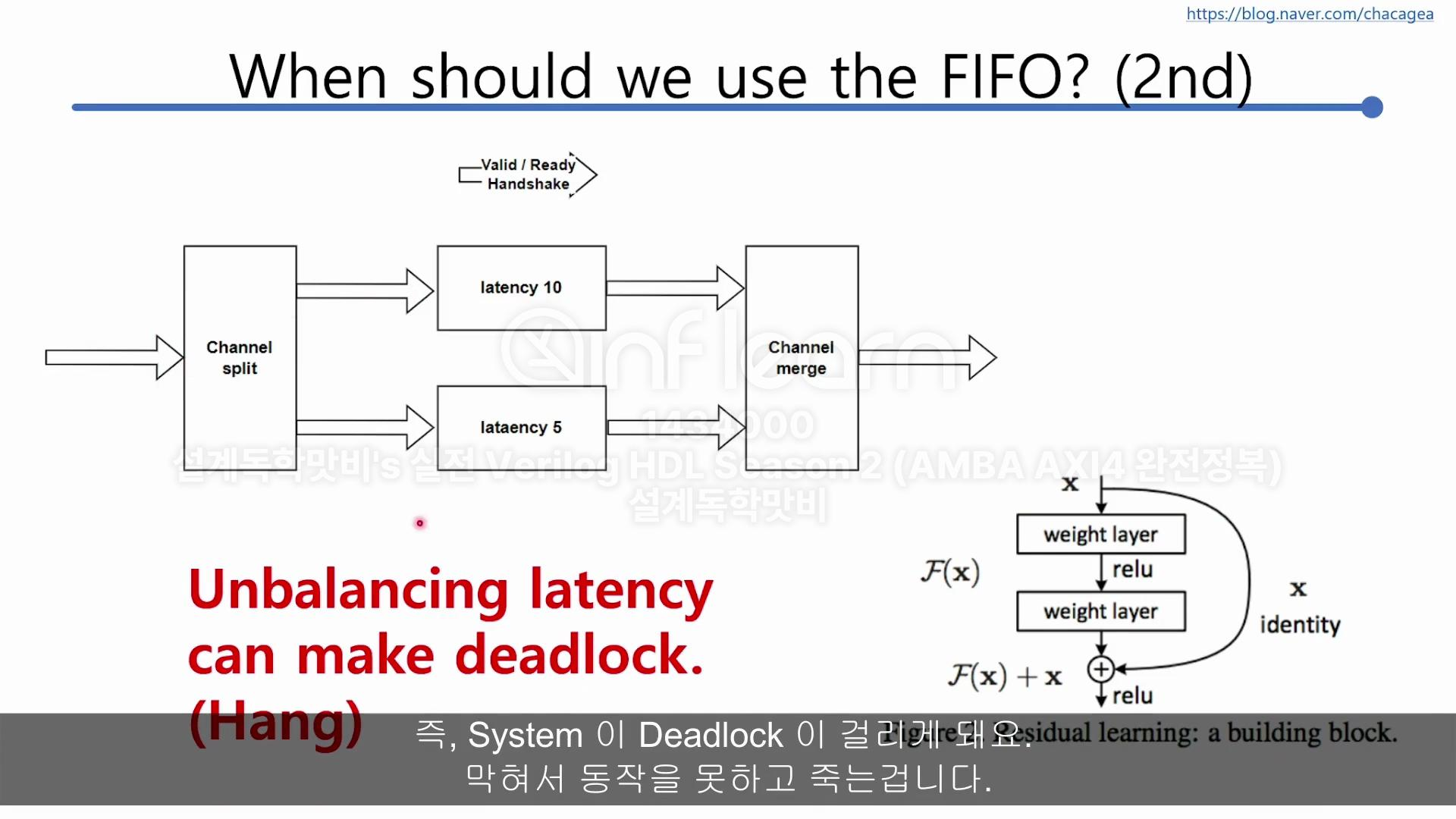

Unbalancing latency can make deadlock부분에서

deadlock이라는 것을 운영체제 과목에서는,

"상호배제, 점유와 대기, 비선점, 환형대기와 같은 상황이 모두 충족할 때, 발생할 수 있다" 라고 배웠습니다.

제가 생각하기에는 강의 영상에서 나오는 이런 모든 상황이 충족되지는 않아보이는데, 단순 5cycle stall만 발생하면 channel merge하는 것이 문제가 없어 보입니다...

단순히 stall이 발생하는 것과 system상 deadlock이 발생해서, 다음 step으로 아예 나아가지 못하는 것에는 큰 차이가 있다고 생각합니다.

HW상에서 deadlock이 발생할 수 있는 명확한 예시가 있을까요?

감사합니다.

답변 1

0

오.. 혹시 매드님? 이신가..?요..?

질문이 고차원 적이시라 ㅎㅎ 제가 알고있는 수준 내에서 답변드릴께요.

먼저 운영체제의 관점에서 배운 "데드락(Deadlock)"과 하드웨어 설계에서 사용하는 "데드락"의 개념이 조금 다를 수 있습니다. 운영체제에서는 데드락이 발생하기 위해 "상호 배제, 점유와 대기, 비선점, 환형 대기"와 같은 4가지 조건이 모두 충족되어야 하는 상황을 정의하지만, 하드웨어에서는 데이터 경합, 비동기적 신호 흐름, 또는 스케줄링에 의해 생길 수 있는 문제가 더 빈번하게 발생할 수 있습니다.

이 강의는 HW 설계에 초점이 맞춰져 있어서, 운영체제에서 다룬 내용과는 다름을 미리 말씀드려요.

운영체제 까지 나아가는 강의는 아니기에 답은 여기서 줄일께요.

"제가 생각하기에는 강의 영상에서 나오는 이런 모든 상황이 충족되지는 않아보이는데, 단순 5cycle stall만 발생하면 channel merge하는 것이 문제가 없어 보입니다...

단순히 stall이 발생하는 것과 system상 deadlock이 발생해서, 다음 step으로 아예 나아가지 못하는 것에는 큰 차이가 있다고 생각합니다."

이 부분 질문을 정확하게 이해를 못했는데요.

저는 stall 이 발생한다고 설명을 해드려서.. 제 생각은 영상을 보시면 될 것 같아요.

혹시 왜 stall 이 발생하지 않는다고 생각하셨는지, 그림하고 같이 설명해주실 수 있을까요?

===================

HW상에서 deadlock이 발생할 수 있는 명확한 예시가 있을까요?

강의에서 예로 설명드린 상황이 있을 것 같아요.

강의에서 다루지 않은 부분은 GPT 답변을 참고 부탁드릴께요. (강의 안에 다룬 내용 같기도 하네요)

HW에서 Deadlock이 발생하는 명확한 예시

하드웨어 설계에서 데드락이 발생할 수 있는 몇 가지 명확한 예시를 들어보겠습니다.

Shared Resource Wait: 예를 들어, 두 개의 모듈(A와 B)이 서로의 출력을 입력으로 받아야 하는 상황이 있다고 가정합시다. 모듈 A는 모듈 B의 출력을 기다리고 있고, 모듈 B는 모듈 A의 출력을 기다리는 경우, 상호 기다리는 상황이 되면서 데드락이 발생합니다.

Pipeline Stall Accumulation: 파이프라인 구조에서 특정 스테이지에서 계속해서 데이터가 차단되거나 비워지지 못하는 상황이 발생할 수 있습니다. 예를 들어, 파이프라인의 앞 단계(Stage 1)에서 데이터가 나가야 하는데, 뒤 단계(Stage 2)에서 데이터가 나가지 못하고 막히게 되면 Stage 1도 멈추고, 결국 전체 파이프라인이 멈추는 상황이 됩니다.

Resource Contention in NoC (Network on Chip): 여러 개의 프로세서나 모듈이 NoC를 통해 데이터를 주고받을 때, 각 모듈이 경합하는 자원이 공유되거나 경합할 때 데드락이 발생할 수 있습니다. 예를 들어, 프로세서 A가 메모리 B로 데이터를 전송하려고 하는데, 동시에 메모리 B가 프로세서 A로부터의 요청을 기다리는 경우 경합이 발생하여 더 이상 진행하지 못하게 됩니다.

0

안녕하세요 답변 감사합니다.

조금 더 명확하게 질문하기 위해 답글을 남깁니다.

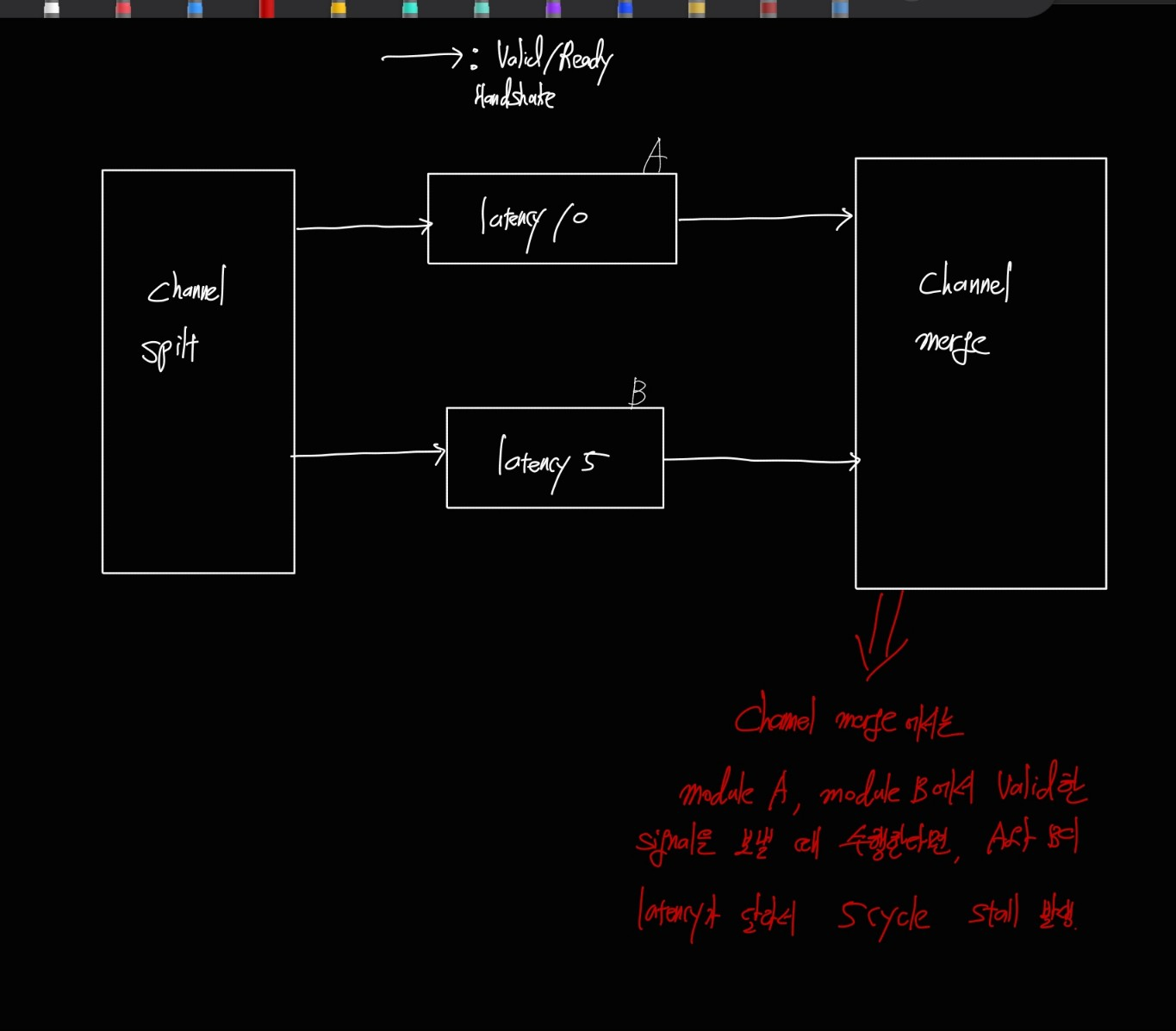

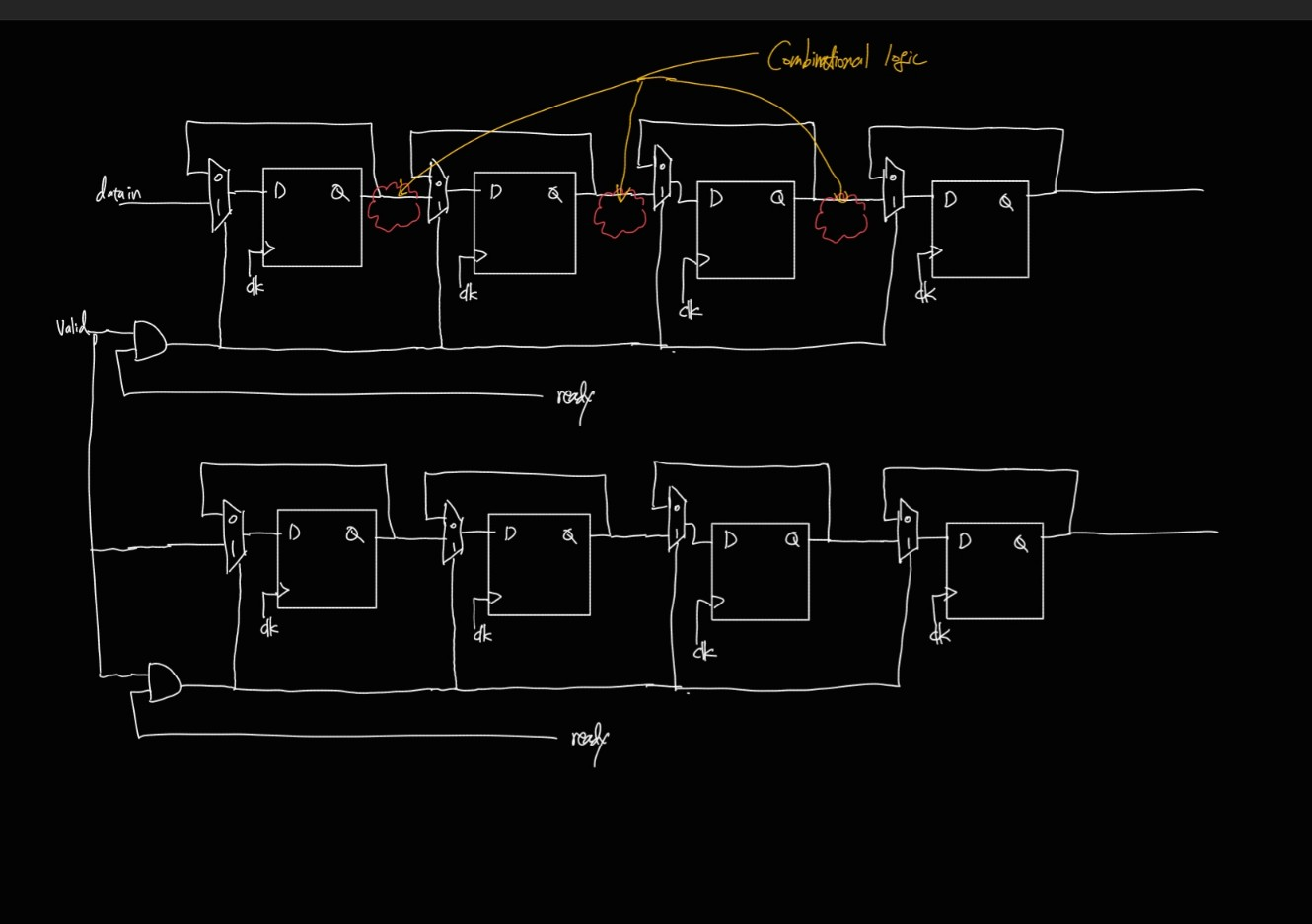

위의 그림이 제가 생각하는 내용인데, 각 module간 연결이 valid/ready handshake로 이어져있으니,

channel merge module에서는 A,B가 둘다 valid 신호가 logical 1일 때, ready 신호를 보냄으로써, A,B의 결과를 가져가면 5cycle stall만 발생할 것이라고 생각합니다.

여기서 이런 생각을 또 할 수 있는데, A와 B모듈이 서로 latency가 맞지 않아서 B에서 먼저끝난 data는 clock에 연동된 register상에서 어떻게 5cycle동안 값을 유지하느냐(모듈 A의 결과가 나올때 까지 wait하는 상황)은 valid/ready handshake이므로, Channel merge 부분에서 ready 신호가 나오기 전까지는 B모듈의 출력 register부분에서 출력이 입력으로 다시 feedback해줌으로써 timing을 맞출 수 있을거라 생각합니다.. (또한 여기서 굳이 fifo를 사용해야만 하냐라는 생각이 들기도 합니다...)

channel merge부분에서 ready가 나와서 A,B의 결과를 가져간다면, 그 때가 되어야 각 모듈 A,B는 channel split에게 ready 신호를 보낼 수 있다고 생각합니다.

이런 흐름으로 간다면 A모듈의 결과를 5cycle동안만 기다려준다면 다음 입력을 받아서 처리할 수 있는 system이 deadlock이 걸린다는 것이 다소 이해가 되지 않습니다.

이 부분은 강의 11분 06초에 나오는 부분인데, 이 그림에서 system이 deadlock이 걸린다는 부분이 저에게는 이해가 되지 않습니다..

조금 두서가 없군요 제 질문이...

정리하자면 다음과 같습니다.

11분 06초에 나오는 강의에 나오는 system이 deadlock이 아닌 5cycle stall이 발생하는 것 아닌가요?

11분 06초에 나오는 system에서 deadlock이든, stall이든 꼭 fifo를 위한 h/w를 배치해야하는가요? valid/ready handshake를 사용한다면 fifo를 사용하지 않고 충분히 unbalancing latency 문제를 해결할 수 있지 않을까요..? (위에서도 언급했듯이, channel merge에서 ready signal을 A,B에서 둘다 result가 나올 때 1로 출력함으로써)

조금 두서가 없군요.. 저도 맛비님 강의base로 계속 공부를 하는데, 제가 강박?이 좀 있습니다..

굳이 써야하나? 혹은 꼭 필요한가? 라는 생각을 항상 던지면서 문제를 해결하다보니...(설계할 때 자원낭비를 최대한 안하고 싶어서 그런거 같습니다..)

위에서 HW상에서 deadlock이 발생할 수 있는 명확한 예시에 대해서는 확실하게 이해가 갑니다.

감사합니다.

0

안녕하세요 🙂

설명 감사합니다. 어떤 부분인지 이해 했습니다.

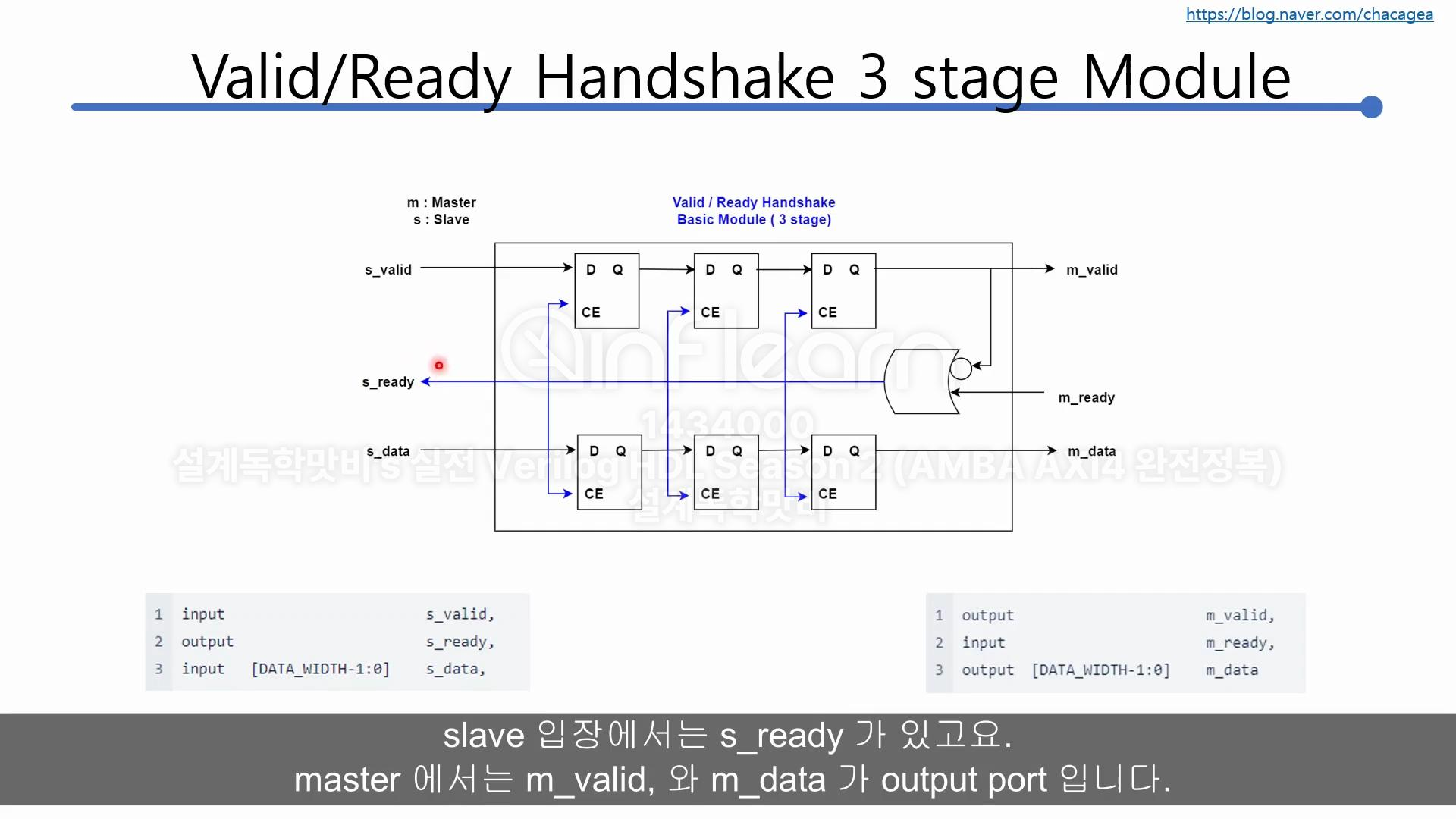

이 부분은 HW 설계할때, waveform 을 1 cycle 단위로 보시면 이해가 빠르긴 한데요.

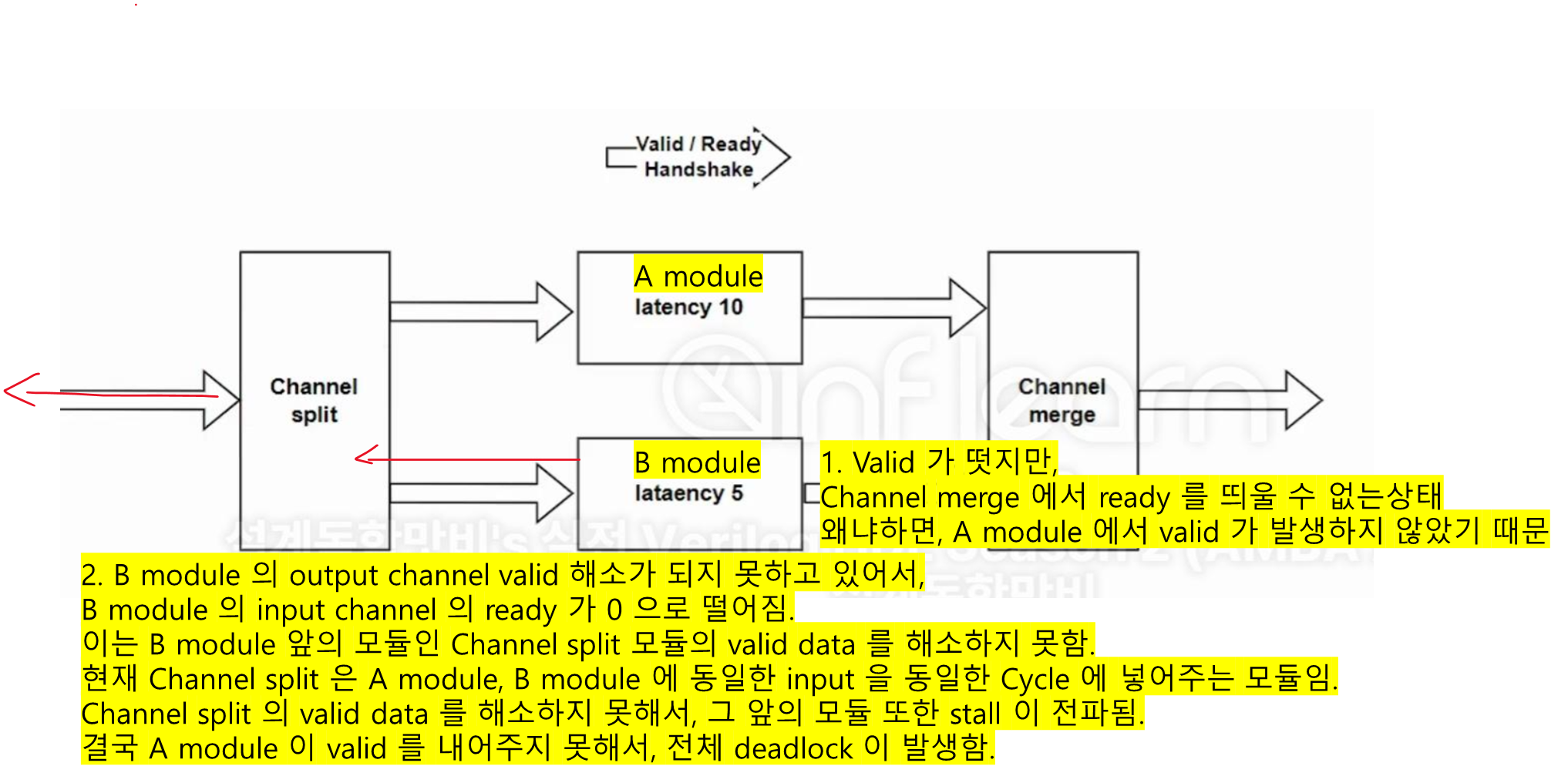

Channel Merge 라는 모듈은,

다음 그림처럼, A 모듈의 입력과 B module 의 입력이 준비되어야 merge 를 해서 하나의 channel 로 출력되게 됩니다.

Channel Split 은 A, B module 에 동일한 input 을 동일한 cycle 에 넣어주는 모듈입니다.

5 cycle 이 지났다고 가정해 보겠습니다.

A module 의 valid 한 data 는 다시 5 cycle 이 지나야 준비가 될텐데요.

여기서 문제는

Channel split 이라는 모듈이 동일한 Valid 입력을 넣어주게 된다는 것입니다.

즉, B module 에서 valid 가 해소되지 않았기 때문에, B module 의 input channel 의 ready 는 0 으로 떨어지게 됩니다.

이는 곧 Channel split 의 valid 를 해소해주지 못하는 상황이 벌어집니다.

이는 A module 의 입력을 막아버립니다. 5 cycle 의 input 이 더 들어와야하는 상황인데 말이죠.

그래서 전체 적으로 deadlock 이 걸려서 HW 모듈이 정지하게 됩니다. (5 cycle stall 이후에 해소되지 않습니다. HW 가 멈춰버려요)

이는 reset 말고는 해소할 방법이 없어요.

이 현상을 현업에서는 hang 이라고 부릅니다.

1

안녕하세요 맛비님 답글 감사합니다.

이해 못 하는 제가 문제가 있는 듯하여...

이전 강의와 지난 FPGA 1장 내용을 다시 보는 도중..

저의 부족함으로 이런 멍청한 질문을 하였군요...

이 그림 보자마자 바로 바보 도 트는 소리가 나왔습니다.

맛비님 계시는 곳에 들렸을지 모르겠군요...

위 그림을 아래와 같이 다시 그려보았습니다.

아마 강의 내용이 이런 의도로 말씀하신것이 아닌가하여..

이렇게 각 module을 그리니, 초기 5cycle이 지나고 split에서 module B로 인하여 valid신호가 끊어지고,

다음 stage로 나아가지 못하고 결국 reset말고는 해답이 없는 deadlock이 올 수 밖에 없다는 결론에 다달았습니다.

위 그림처럼 그리니, module A가 초기 5cycle 이후 아무것도 할 수 없는 구조가 되는군요..

이렇게 깨달은 것이 맞을까요? 맛비님

1

안녕하세요 맛비님

답변감사합니다.

직접 test module을 만들고, 올려주신 testbench를 이용해서 deadlock이 발생하는 것을 직접 waveform을 보니까 이해가 갑니다.

결국 중요한건 parallel하게 배치한 모듈간의 latency를 똑바로 안 맞추어준다면, 당연히 동작도 이상하게 될 것이고, 더구나 채널간에 depandency가 있는 경우에는 회로의 동작이 멈추어 버리는 deadlock이 발생한다는 것을 직접해보니까 확실하게 알게되었습니다...

[HDL 32장-2부] 참고 링크 관련

1

38

2

[HDL 22장] F/F CE 관련 질문

1

47

2

13강에 언급된 강의 내용 질문

1

62

2

22장 vaild/ready

1

99

1

output, reg 선언

1

82

3

gvim

1

65

1

fifo의 stall과 퍼포먼스 드랍

1

60

2

Design Valid I/F

1

75

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

93

2

IDLE state의 시점관련

1

65

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

110

3

[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

1

72

2

system verilog 사용이유.

1

133

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

115

2

다이어그램 이해

1

74

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

76

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

91

3

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

115

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

130

1

예외처리 관련 질문

1

79

2

AXI의 ID의 역할은?

1

191

2

28장 강의 AXI 이론편관련질문

0

113

1

37장 Data bit width 질문

1

60

2