SPI master testbench 질문

327

작성한 질문수 4

안녕하세요! SPI contoller ch.5 소스 코드에서 궁금한 점이 있어 질문 남깁니다.

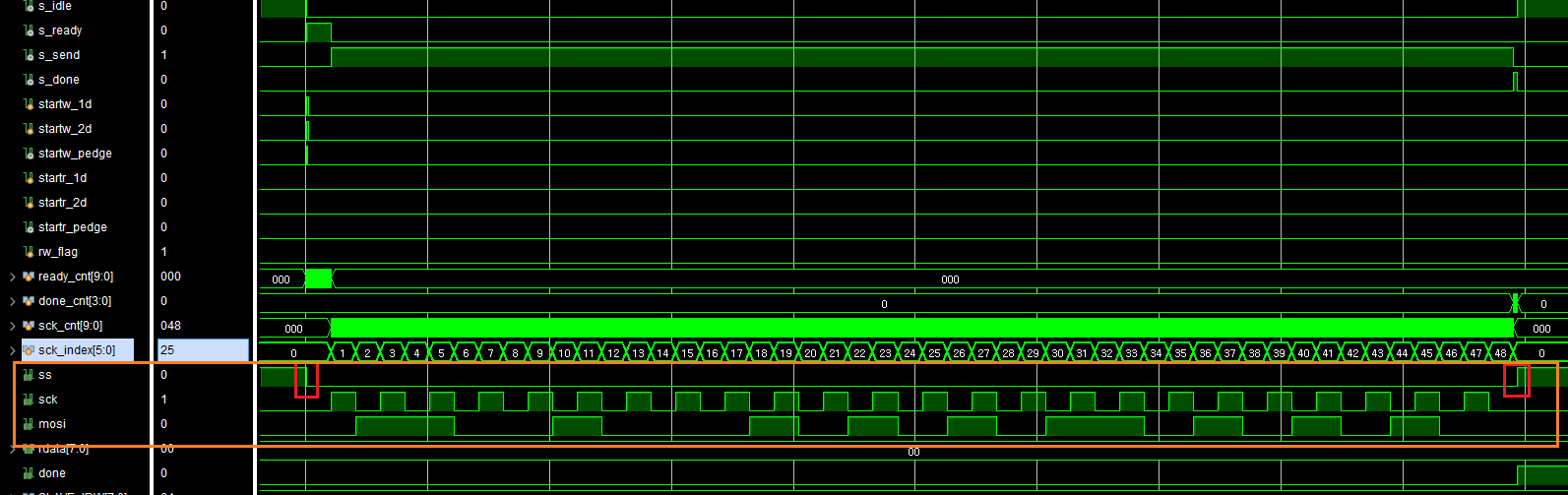

timing 규격상 sck_index 값이 48일 때 send -> done 로 transition이 일어난다고 알고 있는데요

49까지 count 되는 경우에 delay 문제가 없는지 궁금합니다.

감사합니다.

답변 1

0

안녕하세요.

sck_index 값은 ss, sck, mosi 신호 생성을 위한 내부 신호입니다.

따라서 sck_index값이 1-clock 동안 잠시 49로 바뀌었다가 다시 0로 바뀌는 것은 전혀 문제가 되지 않습니다.

그러나 주의해야 할 것은 sck_index 값이 1-clock 동안 49로 바뀌는 것으로 인하여 ss, sck, mosi 신호가 잘못된다면 주의해야 합니다. 예를 들어 sck, ss가 1-clock 동안 1로 바뀐다거나(불필요한 신호가 생성됨) 한다면 이는 잘못된 것이기 때문에 그 부분이 발생하지 않도록 처리해 주어야 합니다.

아래는 ss, sck, mosi의 전체 파형을 보여줍니다. 전체 파형은 이상없이 잘 동작하고 있기 때문에 문제가 되지는 않습니다.

(사실 ss 신호가 좀 더 일찍 H->L 로 바뀌거나, 좀 더 늦게 L-H로 바뀐다고 해도 문제가 되지는 않습니다. spi slave에서 신호를 받아서 처리할 때에는 sck보다 높은 주파수(main clock)로 처리하기 때문입니다. 강의에서도 spi master를 구현하는 clock은 100Mhz를 사용합니다)

감사합니다 ~!!

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

33

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

Verilog 코딩 스타일

0

119

2

xilinx 권고와 차이

0

248

2

강의자료

0

115

1

open hardware manager에서 보드 인식 못하는 문제

0

343

2

ifelse, 삼항연산자에 대해서 질문 있습니다.

0

425

1

RAM ip를 이용하여 FIFO 기능을 구현할 수도 있나요?

0

327

1

SPI MASTER 질문

0

248

1

자사 개발보드 관련

0

357

2

안녕하세요. IP Packaging 관련 질문 있습니다.

0

317

1

안녕하세요. verilog 활용 관련 문의드립니다.

0

342

1

안녕하세요 fpga_intro_v16 192p에 질문있습니다!

0

335

1

안녕하세요 SLVAE 컨트롤러에 대한 질문이 있습니다

0

371

1

안녕하세요 I2C Register 모듈에 대해서 질문이있습니다.

0

416

1

SPI에서 Master 내의 miso 값 update 과정에서 질문있습니다.

1

878

1

안녕하세요 i2c master 부분에 관련하여 질문있습니다.

0

612

1

SPI Master 부분 질문입니다.

1

612

3

I2C Master 모듈관련 질문입니다.

0

1182

1

memory configuration

0

841

1

UART, SPI구현

0

657

1

SPI와 I2C의 차이

2

1981

1