SPI에서 Master 내의 miso 값 update 과정에서 질문있습니다.

안녕하세요. FPGA_intro_v16.pdf 파일 내의 chapter 6.2.3에서 질문이 있습니다.

152-182 line에서,

miso의 값을 update하는 과정에서, freq=100이라고 한다면, SLAVE_ID[7]이 update 된 후 SLAVE_ID[6]은 90 clock cycle 후에 update 되는 것으로 보입니다.

그 이후에는 200cycle마다 SLAVE_ID[6] ~ wdata[0]까지 주기적으로 update 되는 것으로 보입니다.

제가 코드를 잘 해석한 것이 맞다면, SLAVE_ID[7]과 SLAVE[7] 사이에서만 주기성이 깨진(?) 것으로 보이는데 이는 ready state에서 data를 한 bit라도 미리 보내서 s_send에서 소모되는 clock cycle을 조금이라도 줄이기 위함인지, 다른 특별한 목적이 있는지, 저의 해석이 틀린 것인지 궁금하여 질문드립니다.

답변 1

1

spi master는 SM (State Machine)으로 동작합니다.

- s_idle

- s_ready

- s_send

- s_done

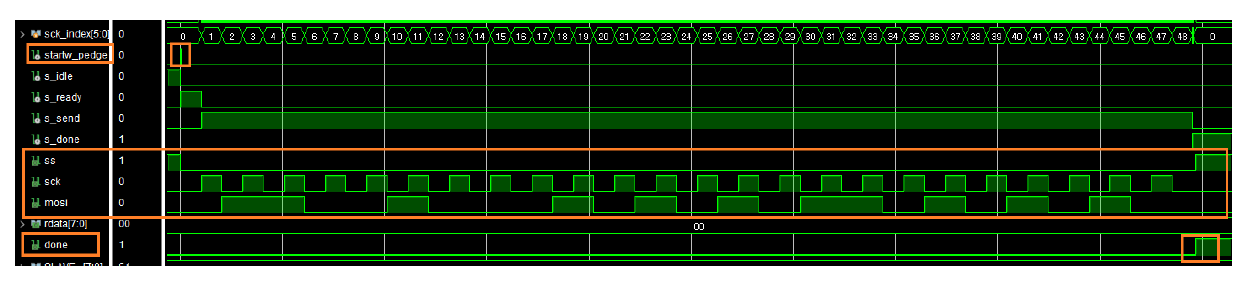

s_ready 상태에서는 spi 전송을 시작하는 상태입니다. 즉 ss 신호를 0로 만들어주고, mosi의 첫번째 데이터 (slave_id[7])을 전송하고, sck 신호를 0로 만들어 줍니다.

sck, mosi 의 실제 데이터는 s_send 상태에서 전송됩니다. s_send 상태에서는 일정한 간격으로 sck, mosi 신호를 전송하게 됩니다. 문서의 51 페이지를 보면 simulation 파형이 있습니다. 그 파형을 참조하시길 바랍니다.

slave_id[7]을 전송하고 slave_id[6]을 전송하는 시간과 slave_id[6]을 전송하고 slave_id[5]을 전송하는 시간이 mclk 기준으로 몇 clock 차이가 있긴 하지만, 중요한 것은 sck 가 일정한 시간으로 전송되고, mosi 신호는 sck가 0 일 때 전송되는 것입니다.

spi master 규격에서 ss가 Active 되고 몇 clock 후에 sck가 전송되는지는 따로 규격이 없고, 사용자가 알맞게 구현하면 됩니다.

코드를 SM으로 구현하는 것은 매우 좋은 방법입니다. 이러한 부분을 익히고 사용하시길 바랍니다.

감사합니다.

0

제가 FPGA에 대한 배움이 짧아 이해되지 않는 부분이 있습니다.

mosi 신호는 sck가 0일 때 전송되는 것이 중요하다는 의미는, flip-flop처럼 sck의 negedge 혹은 posedge일 때 마다 전송되는 주기성을 갖도록 하는 것이 중요하단 의미일까요? 아니면, latch 처럼 sck가 low일 때 전송되는 것이 중요하다는 의미일까요?(이 경우 sck가 high일 때 전송되어선 안되는 것인가요?)

또한, SLAVE_ID[7]을 s_ready에서 전송하는데, 이 첫 번째 data만 s_ready 에서 전송하는 특별한 이유가 있는 것인지, 아니면 s_ready에서 전송하는 SLAVE_ID[7]을 s_send에서 전송하도록 하여 s_send 에서 전송하는 data를 한 주기씩 delay시켜 sck_index를 49까 세도록 확장하여 주기성을 갖도록 구현해도 상관없는지 궁금합니다. (line 157을 지우고, sck_index==6'd1에서 SLAVE_ID[7] 전송, sck_index==6'd3 에서 SLAVE_ID[6] 전송 .....)

주말인데도 친절히 답변주셔서 정말 감사드립니다.

1

spi 규격서를 보면, mosi 신호는 sck 신호가 low 구간에서 변하고, sck 신호가 High 구간에서는 변하면 안됩니다. 즉 spi slave 에서 데이터를 수신할 때에는 sck가 High 구간에서 데이터 값을 읽게 됩니다. (spi 규격서를 찾아보셔셔 spi 통신의 기본개념을 이해하셔야 합니다)

SLAVE_ID[7]을 s_send 구간에서 전송해도 됩니다. 다만 스펙에 맞게 (or 위의 simulation 파형)에 맞게 구현해야 합니다.

이를 구현하기 위해서는 먼저 49페이지에 있는 타이밍 다이어그램을 수정해서 s_send 구간에 s7 데이터가 전송하도록 수정하고, 거기에 맞게 코드를 구현하면 됩니다.

verilog 코드는 눈으로 머리로 구현되지 않습니다. 먼저 49 페이지에 있는 것과 같이 자신이 구현하려는 타이밍 다이어그램을 구성하고 거기에 맞게 구현합니다. 한번에 모두 다 구현할 수는 없고 조금 구현하고 맞는지 중간 중간에 simulation으로 확인하고, 또 코드 구현해서 타이밍 확인하고 이러한 과정을 반복해서 구현하게 됩니다.

verilog, fpga를 배우시려면 인내심을 가지고 조금씩 조금씩 알아가시길 바랍니다. 코드를 눈으로 이해하려고 하면 한계가 있습니다. 저도 제가 만든 코드라도 눈으로 다 이해할 수 없습니다. simulation으로 타이밍 확인하면서 코드와 비교하며 확인합니다. 처음에는 대충 흐름을 파악한다고 해도, 결국 verilog를 배우려면 직접 simulation 하며 분석하며, 조금씩 수정해가며 배우는 방법밖에 없습니다.

[HDL 32장-2부] 참고 링크 관련

1

39

2

강의 만료일 연장 신청

0

42

2

기초예제 파일 불러오기 문의

0

30

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

33

2

Verilog 코딩 스타일

0

120

2

xilinx 권고와 차이

0

251

2

강의자료

0

115

1

open hardware manager에서 보드 인식 못하는 문제

0

350

2

ifelse, 삼항연산자에 대해서 질문 있습니다.

0

425

1

RAM ip를 이용하여 FIFO 기능을 구현할 수도 있나요?

0

327

1

SPI MASTER 질문

0

249

1

SPI master testbench 질문

0

327

1

자사 개발보드 관련

0

357

2

안녕하세요. IP Packaging 관련 질문 있습니다.

0

317

1

안녕하세요. verilog 활용 관련 문의드립니다.

0

344

1

안녕하세요 fpga_intro_v16 192p에 질문있습니다!

0

336

1

안녕하세요 SLVAE 컨트롤러에 대한 질문이 있습니다

0

371

1

안녕하세요 I2C Register 모듈에 대해서 질문이있습니다.

0

416

1

안녕하세요 i2c master 부분에 관련하여 질문있습니다.

0

615

1

SPI Master 부분 질문입니다.

1

612

3

I2C Master 모듈관련 질문입니다.

0

1182

1

memory configuration

0

843

1

UART, SPI구현

0

657

1

SPI와 I2C의 차이

2

1982

1