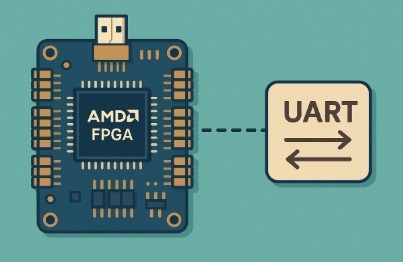

Triển khai UART trên FPGA

EasyFPGA

UART là một phương thức giao tiếp nối tiếp cơ bản và được sử dụng rộng rãi, là một chủ đề học tập rất phù hợp cho người mới bắt đầu tiếp cận thiết kế FPGA. Trong khóa học này, chúng ta sẽ tìm hiểu chi tiết về nguyên lý giao tiếp và cấu trúc khung của UART, sau đó tiến hành quá trình tự triển khai logic truyền nhận thông qua thiết kế RTL (Register Transfer Level) dựa trên hiểu biết đó. Bằng cách triển khai UART trên FPGA, bạn có thể phát triển một cách có hệ thống năng lực thiết kế mạch kỹ thuật số và tích lũy kinh nghiệm kiểm tra hoạt động ở cấp độ phần cứng thực tế thông qua mô phỏng và kiểm định. Ngoài ra, bạn cũng sẽ học cách sử dụng Soft Processor như MicroBlaze và Xilinx UART IP, từ đó hiểu rộng hơn về quy trình thiết kế hệ thống dựa trên bộ xử lý và cấu hình giao diện. Qua đó, bạn có thể trang bị năng lực phát triển toàn diện, bao gồm cả thiết kế logic và thiết kế bộ xử lý.

초급

FPGA, system-verilog, uart