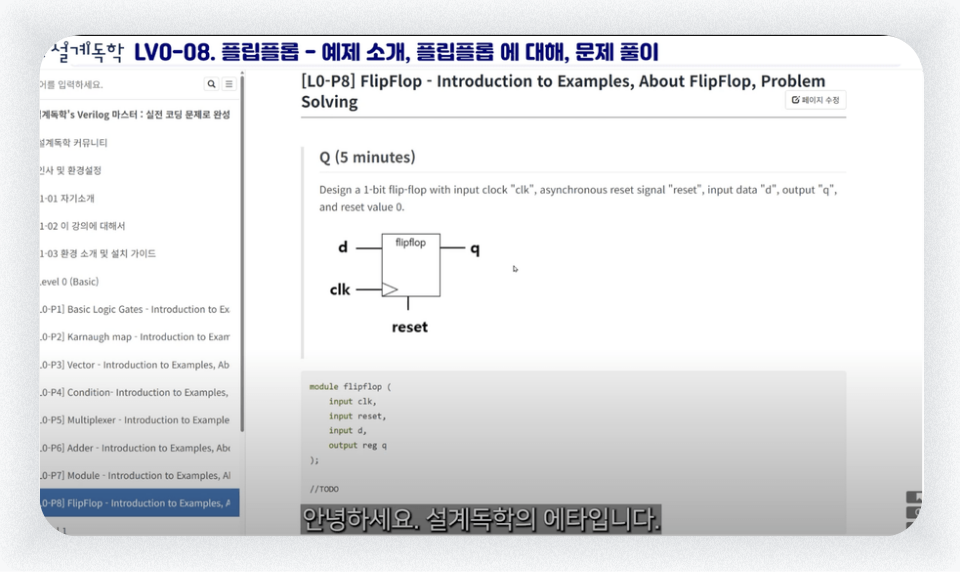

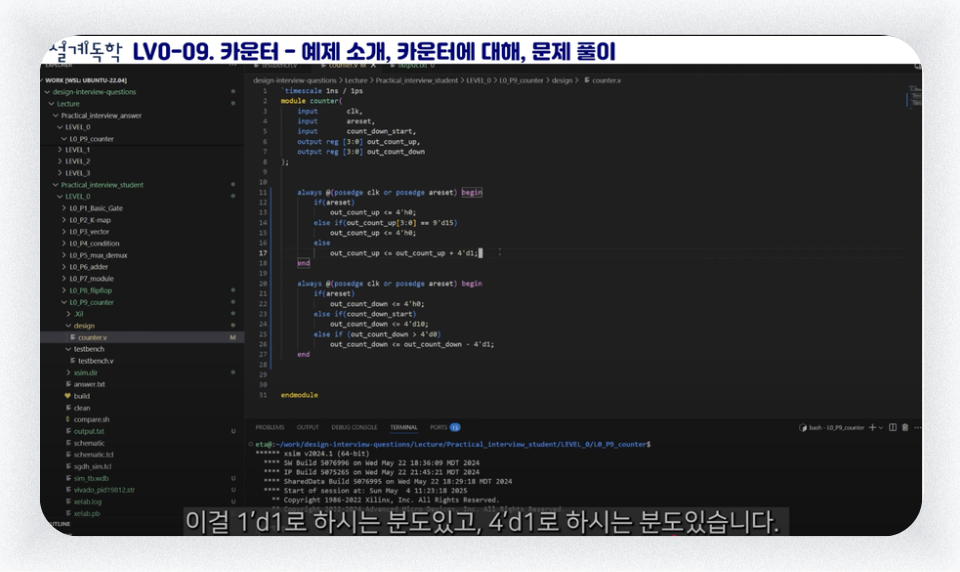

Thực hành Verilog HDL Season 2 của Seolgye Dokhak Matbi (Chinh phục hoàn toàn AMBA AXI4)

semisgdh

Hãy cùng 설계독학 (Tự học thiết kế) tích lũy kinh nghiệm thiết kế AMBA AXI4 - nền tảng của SoC Bus và kiểm thử VIP bằng cách sử dụng Verilog HDL!

Trung cấp trở lên

Verilog HDL, FPGA, amba