챕터5 CNN basic 질문입니다

695

작성한 질문수 3

안녕하세요 좋은 강의 감사합니다.

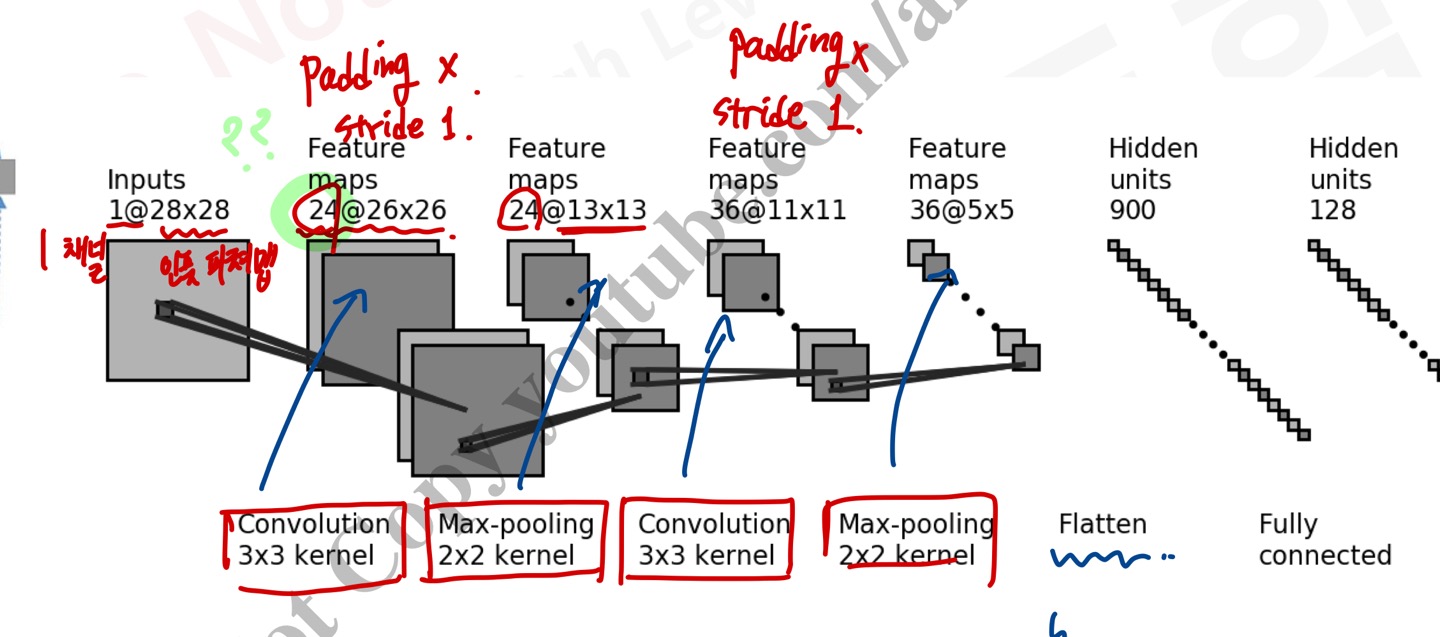

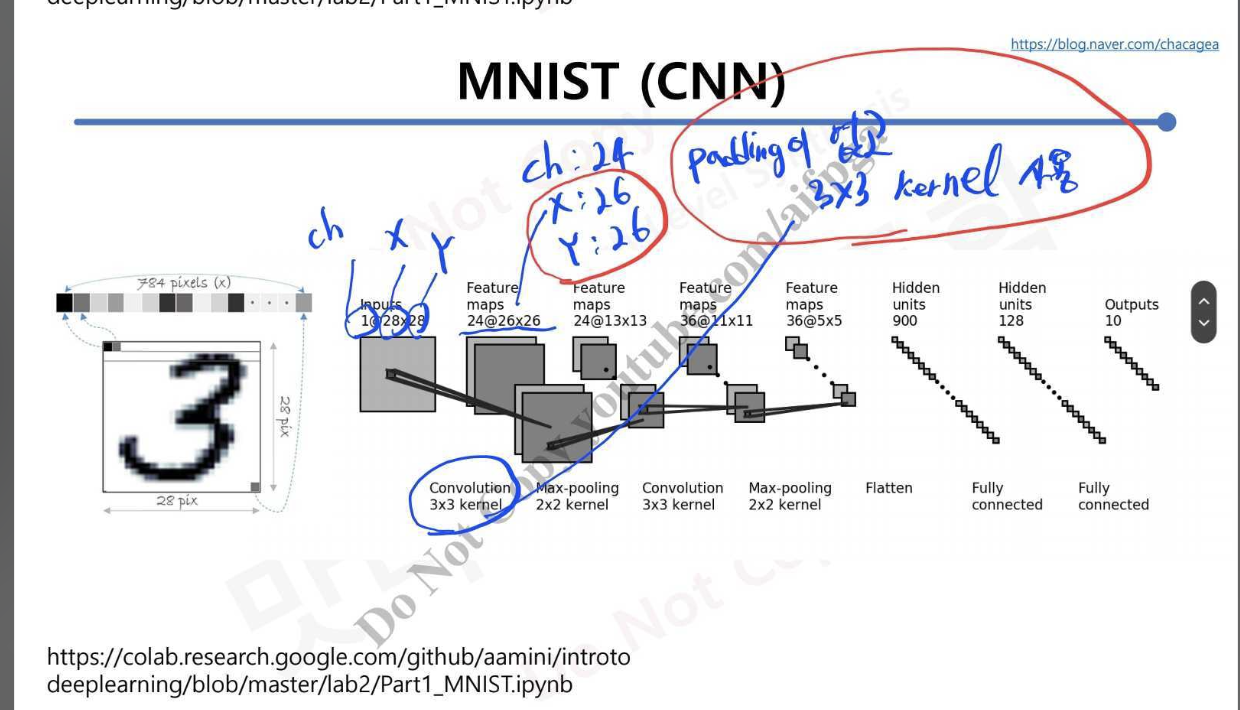

1. 강의내용 중 stride를 설명하실 때 output 피쳐맵의 크기가 X/stride, Y/stride로 일반화가 가능하기 때문에 stride가 1이면 input output featuremap 크기가 동일하다고 설명 해주셨는데, 만약 stride가 1일 때, padding이 없다면 X-2, Y-2만큼의 output feature map이 생기지 않나요? padding이 없다면 컨볼루션 할 때 미정의 값으로 연산을 해야할 것 같아서요..!

2.아래의 그림에서 output 채널의 크기는 예시에서 임의로 주어진 것인지 궁금합니다! output 채널의 크기인 24개 만큼의 depth가 weight에 있다고 가정한 예시일까요?

답변 2

1

저도 동일한 질문인데요.

입력 피처맵이 1@28*28이고 컨벌루션한 결과 출력 피처맵이 24@26*26(채널이 24)인 이유는 컨벌루션 커널 개수가 24개를 사용해서 그런가요?

0

안녕하세요 :)

A1. 알고계신것이 맞습니다. 강의에서 padding 내용을 뺏다면, 실수한거에요 ㅠ

다음과 같은 일반화가 가능합니다.

padding 이 없다.

stride == 1

위와 같은 조건이라면

다음 layer 의 feature map X : X - (Kx-1)

다음 layer 의 feature map Y : Y - (Ky-1)

Q2. 예시에서 임의로 주어진 것인지 궁금합니다! output 채널의 크기인 24개 만큼의 depth가 weight에 있다고 가정한 예시일까요?

A2. 예제로 사용한 Network 는 알고리즘 엔지니어가 설계합니다. 즉 24 개의 의미는 아 그렇구나.. 하시면 될 것 같아요. (왜 24개일까? 가 궁금하신 거라면, Network 설계자에게 물어봐야합니다.)

예시이다. 생각하시면 될 것 같아요.

즐공하세요 :)

[AI HW Lab2] CNN Verilog HDL Practice 1 (Simulation) - 문제설명편 ppt

1

103

2

[AI HW Lab1] CNN Core C 코딩 (Golden Model 만들기)

1

89

2

spartan7 fgga484보드

1

76

1

soft reset관련 질문드립니다!!

1

60

2

예제 코드 환경설정

1

74

2

HW 언어 for loop 해석

1

57

3

수업자료 관련 질문드립니다.

1

75

2

FPGA 기반 ASIC 설계 검증 시 다차원 배열 처리 방식 및 강의 수강 순서 고민

1

104

2

Fpga에 ai 가속기를 사용하는 이유

2

414

2

AI HW 11장 관련 질문드립니다.

1

112

2

소프트 맥스 관련 질문드립니다.

1

202

1

Data형태에 따른 AI가속기 구현 질문

1

221

1

cnn_core simulaiton

2

281

3

zynq z7 10 parameter 크기

1

208

2

ip 패키징 질문

1

285

1

Image 인식 가속 모델을 설계하려면

1

308

2

이 강의 수강을 위해 fpga 구입이 필요할까요?

2

368

2

혹시 AI 관련 강의도 Zybo Board가 필요한가요?

1

291

2

cnn_kernel.v 코드질문입니다.

1

197

1

6장2부 15분 12초 왜 feature map size가 변경되지 않나요?

1

256

2

zybo z7 케이블 관련 질문

1

361

1

CNN layer별 연산

1

272

2

CNN Core에 weight 와 input feature map 관련해서 질문있습니다!

1

259

1

Linux 및 외장 하드 사용에 관한 질문

1

267

2