실행결과와 표 차이

강의 잘 보고 있습니다.

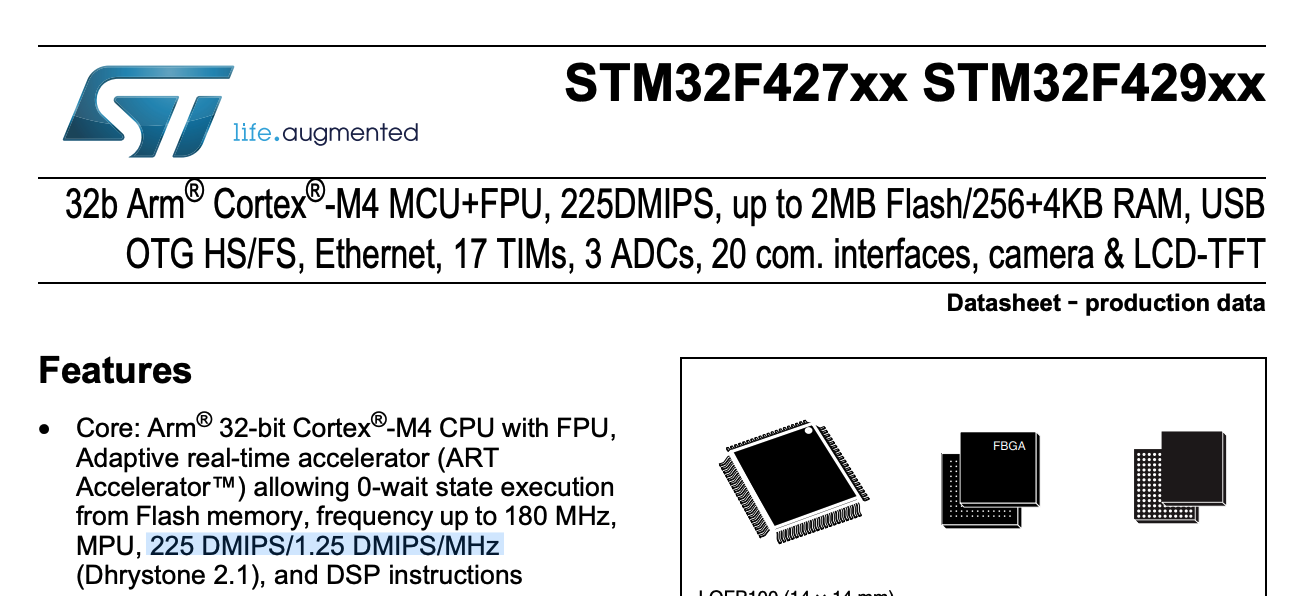

앞서 강의의 표에선 Cortex-M3/M4의 경우 DMIPS/MHz 값이 1.25로 나옵니다.

그렇지만 실험을 통해 DMIPS를 측정했을 때 72DMIPS(180MHz 기준)으로 나오는데 이럴 경우 앞의 표에서 본 값이랑 너무 차이가 큽니다.

문제가 있어보이는데 제가 무엇을 놓치고 있는건가요?

답변 1

0

안녕하세요, 김상현님!

꼼꼼하게 지적해 주셨네요. 덕분에 저도 이러한 실험을 해볼 수 있게 되어 기뻤습니다 ^^

결론부터 말씀드리자면 드라이스톤 벤치마킹은 소스코드를 컴파일하는 최적화 옵션의 영향을 받음을 알 수 있었습니다.

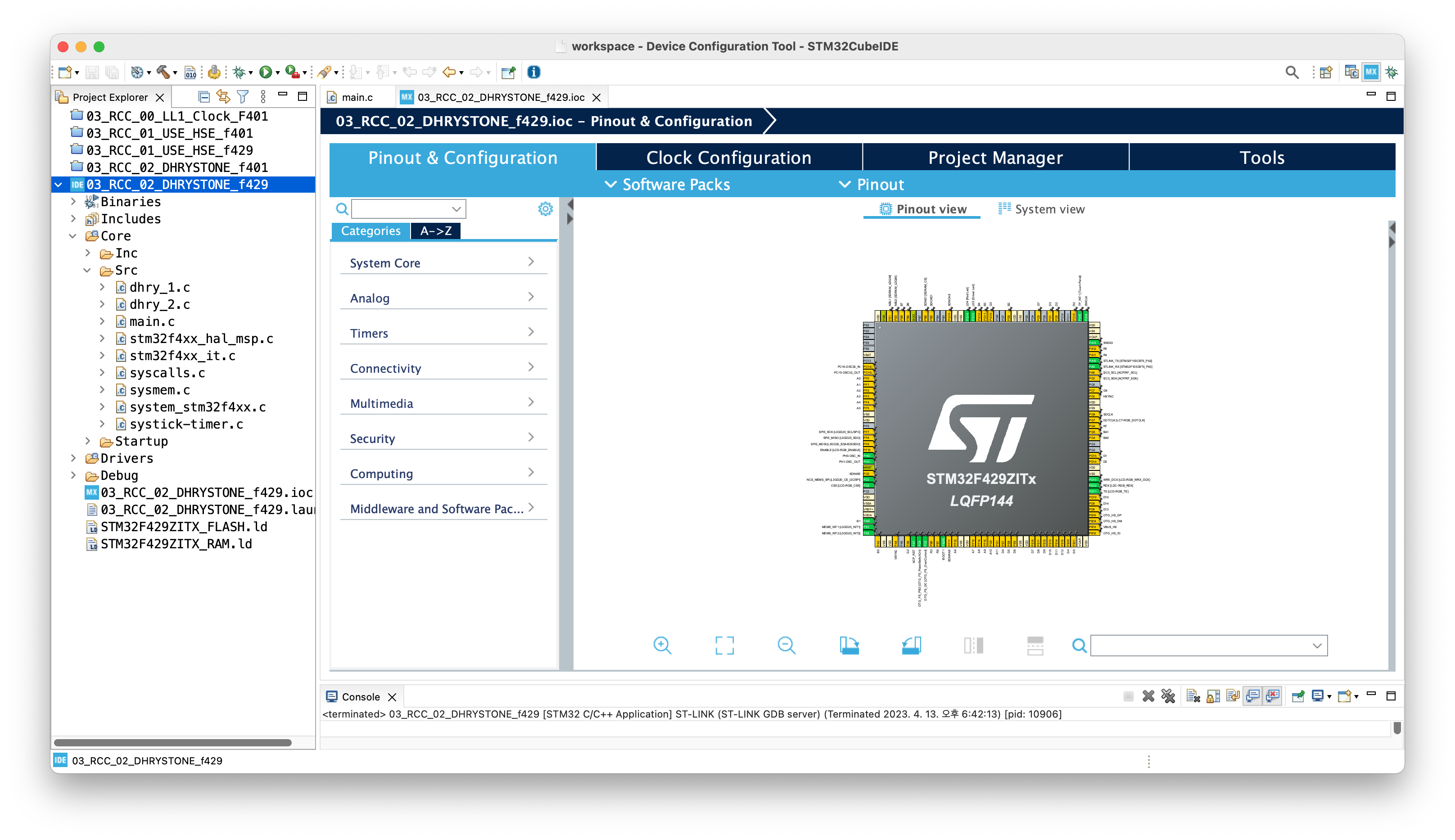

▲드라이스톤 벤치 마킹 프로젝트

▲드라이스톤 벤치 마킹 프로젝트

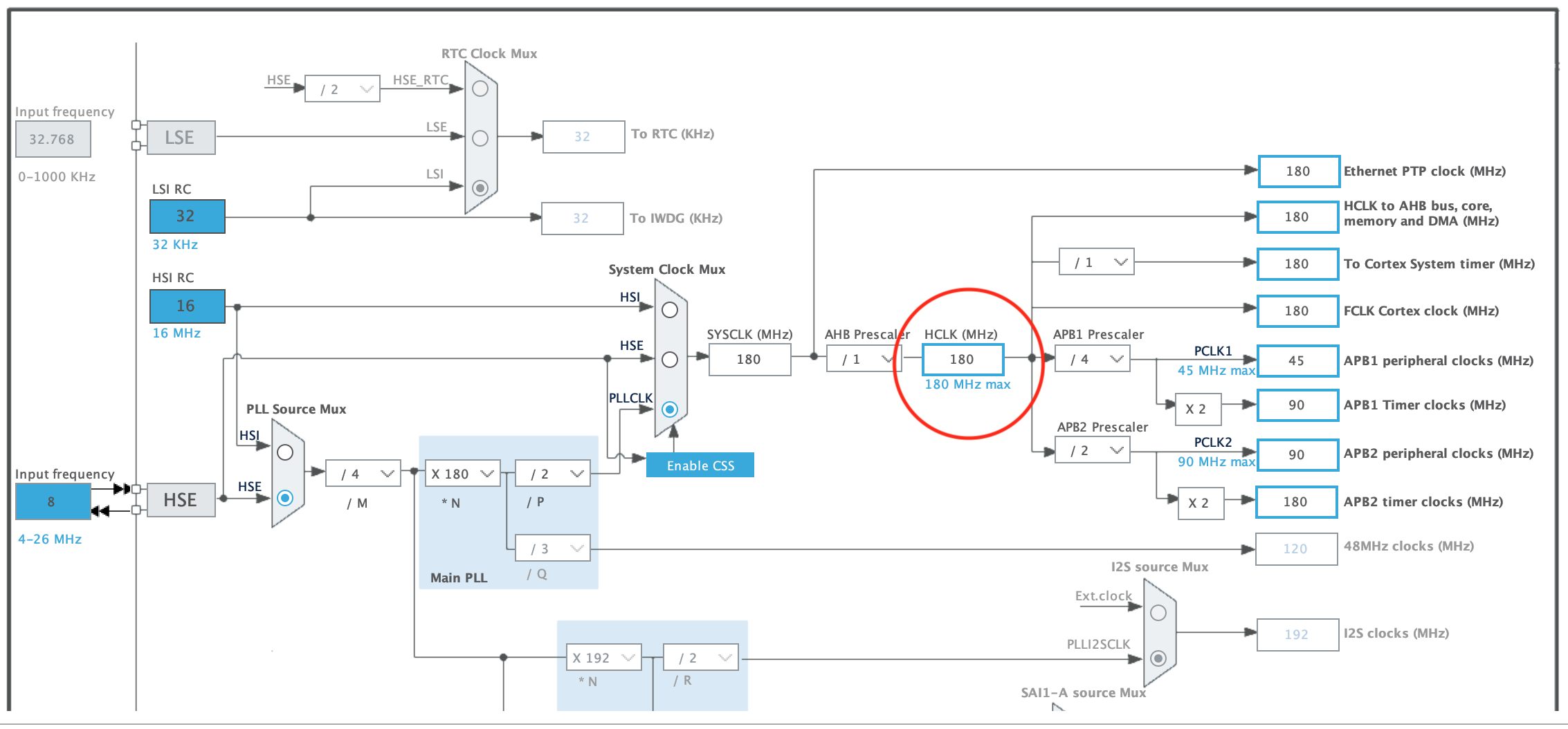

▲클럭 설정

▲클럭 설정

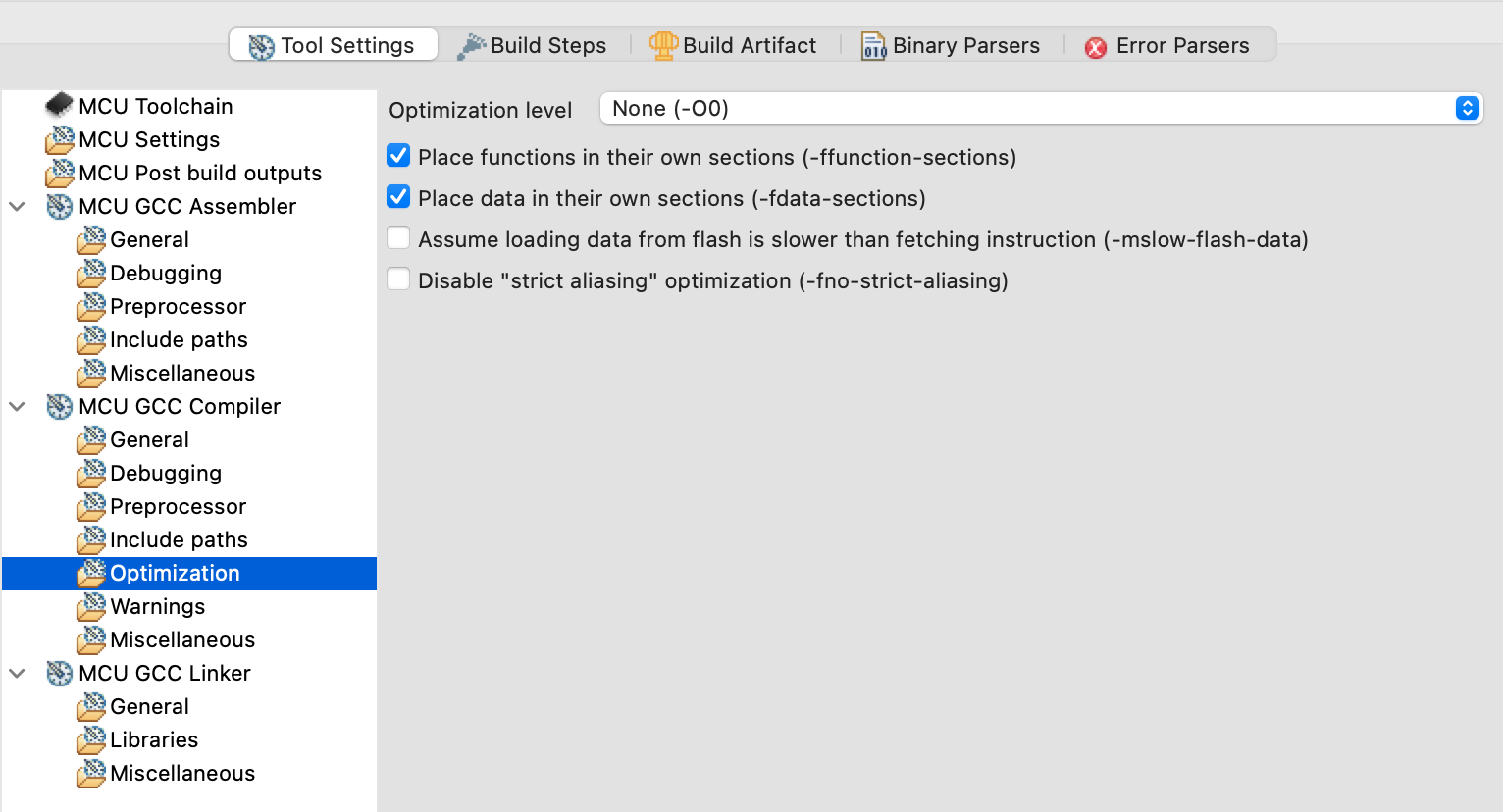

▲ 컴파일러 최적화 설정

▲ 컴파일러 최적화 설정

아래는 테스트 결과입니다

-O0

HELLO, STM32

Benchmarking. Please wait...

1000000 iterations in 7808 ms: 128073/s, 72 DMIPS-O1

HELLO, STM32

Benchmarking. Please wait...

1000000 iterations in 3785 ms: 264200/s, 150 DMIPS-O2

HELLO, STM32

Benchmarking. Please wait...

1000000 iterations in 2707 ms: 369412/s, 210 DMIPS-O3

HELLO, STM32

Benchmarking. Please wait...

1000000 iterations in 2851 ms: 350754/s, 199 DMIPS

마무리

드라이스톤 v2.1 환경에서 STM32CubeIDE 최적화 옵션을 -O2 로 설정하고 컴파일 & 실행하면 210 DMIPS (@180Mhz) 의 실험 결과를 보여주었습니다. 데이터 시트의 결과(225 DMIPS) 와 큰 차이가 없는 것을 확인할 수 있습니다.

데이터 시트에 나온 225 DMIPS 는 MAX 180MHz 에서 테스트한 결과로 짐작됩니다.

결론입니다. 소스코드 및 컴파일러 최적화: 벤치마크를 실행하는 소스코드와 컴파일러의 최적화 수준에 따라 성능 결과가 크게 달라질 수 있습니다. 이러한 차이로 인해 측정된 DMIPS 값이 ARM의 공식 값과 다를 수 있습니다

stm32cubeide 관련 문의

0

46

2

DMA 관련한 강의도 제작해주실 수 있으신가요 ?

0

95

1

그림들도 해석 할 수 있어야 하나요?

1

100

2

no-stlink

1

80

2

4개의 CPU 사이클이 필요한 이유

1

100

2

MAC으로 진행 질문드려요..

1

95

2

학습 진행 시, 사용하는 Board에 대한 문의 드립니다!

0

159

2

push pop 질문

1

190

2

STM32Fx Cortex ARM 프로그래밍 저자:홍봉조, 출판사:지식과 감성

0

242

1

CORTEX_02_ASSEMBLY 빌드시 에러

1

270

1

외부 ST Link 연결 이용한 SWD 방법

0

339

1

파이프라인과 명령어

1

327

1

명령어 fetch

0

238

1

lr 레지스터 LSB 값

1

258

1

Disassembly 창 문제

0

349

1

s702 강좌에서 사용한 technical reference manual 문서

1

325

1

s702에 원자적 Access 를 위한 BSRR 코드작성 부분에 대해서

1

271

1

s202 LED 점등 예제 실행시 에러

2

351

1

STM32F429I-DISC 보드의 펌웨어

2

394

1

제공되지 않은 강의교재

0

319

1

s524 테일체이닝 강의 질문

0

234

1

부트코드와 부트로더의 차이점

1

1525

1

메모리 맵 질문

0

280

1

xPSR 레지스터 플래그 값 및 기타 질문 드립니다.

1

862

2