4개의 CPU 사이클이 필요한 이유

99

작성한 질문수 28

안녕하세요 질문이 있어 글 남깁니다.

플레시메모리 읽기 작업은 한번에 128비트를 읽을 수 있다로 이해했는데 왜 순차코드의 경우 명령줄을 실행하려면 적어도 4개의 CPU사이클이 필요한지 잘 모르겠습니다.

첫번째 클럭에 128비트를 한번에 다 읽을 수 있는건가요?

아니면 128비트를 읽는데 4사이클로 나눠서 읽는다는 건가요?(1사이클에 32비트씩)

이 128비트를 읽는게 'FETCH' 랑은 다른건가요?

CPU4개의 사이클 동안 플레시메모리 버퍼가 채워진다고 하셨는데, 한번에 128비트를 읽을 수 있다고 했는데 이 한번이 한 사이클이 아닌건가요?

앞서 하버드 구조로 순차적으로 한 클럭에 동시에 F, D, E가 수행될 수 있음은 이해했습니다.

답변 2

0

안녕하세요. 이명운님!

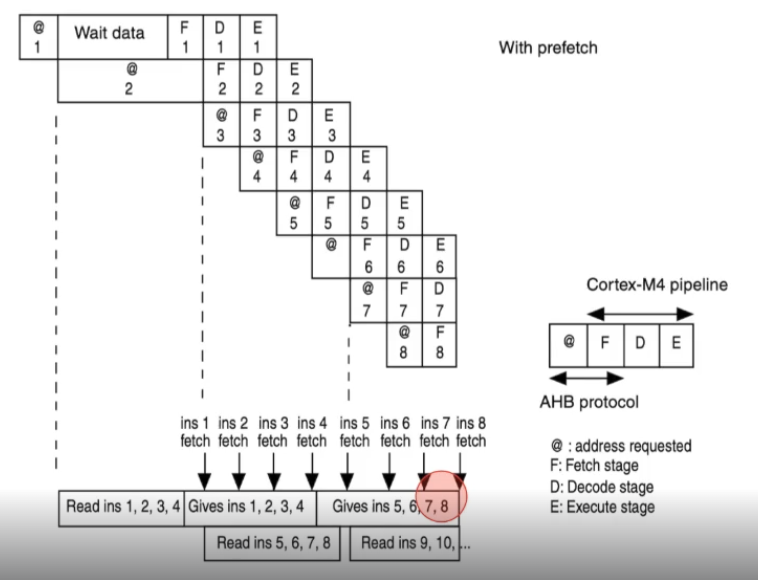

STM32 플래시 메모리는 CPU 성능에 보조를 맞출수 있도록 128비트 가속기 인터페이스를 채택하고 있습니다. 데이터 시트에는 플래시 메모리의 128비트를 버퍼에 채우는데 버스클럭 기준 1클럭이 필요한지 4클럭이 필요한지에서 대해서는 명확한 설명은 없습니다. 다만 아래 그림을 참고해 유추해보면 4클럭 단위로 버퍼를 채우는 것으로 생각해도 좋을 것입니다.

CORE 는 이 버퍼에서 명령어들을 페치합니다. 플래시 가속기는 버퍼가 비워지면 준비한 다음 128비트를 버퍼에 채우는 식으로 동작하는 것을 아래 그림에서 확인해주세요.

0

안녕하세요, 인프런 AI 인턴입니다. 이명운님!

플래시 메모리에서 데이터를 읽는 과정은 주로 CPU와 메모리 간의 인터페이스 속도로 인해 여러 클럭 사이클에 걸쳐 진행됩니다. 128비트를 한번에 읽는다면 이는 메모리 인터페이스에서 한번의 데이터 전송으로 가능한 최대량을 의미합니다. 그러나 다음과 같은 이유로 여러 사이클이 필요할 수 있습니다:

인터페이스 병목: CPU와 메모리 간의 데이터 전송 속도가 클럭 속도와 일치하지 않을 수 있습니다. 따라서 각 사이클에서 읽혀진 데이터가 CPU에 맞춰 처리되어야 합니다.

버스 대역폭의 한계: 실제로 데이터 전송은 물리적 버스의 용량에 따라 나뉠 수 있습니다. 128비트를 한 번에 읽는다고 하더라도 내부적으로 다단계의 과정을 거칠 수 있습니다.

파이프라인 처리: CPU에서 명령어를 읽고 처리하는 과정은 페치(Fetch), 디코드(Decode), 실행(Execute) 단계로 나뉩니다. 이 과정 중 특정 명령어가 여러 사이클에 걸쳐 진행되며, 파이프라인 특성상 여러 단계가 동시에 이루어지기 때문에 각 사이클에서 명령어 큐가 채워지는 것이 필요합니다.

이제 관련 답변이 포함된 질문 URL들을 소개해드리겠습니다:

-

- 이 질문에서 플래시 메모리가 128비트 단위로 동작하며 처음 128비트를 읽는 시간 동안 CPU가 실제로 파이프라인 ‘FETCH’ 단계에서 아무것도 할 수 없다는 과정을 설명합니다.

- 이 질문에서 플래시 메모리가 128비트 단위로 동작하며 처음 128비트를 읽는 시간 동안 CPU가 실제로 파이프라인 ‘FETCH’ 단계에서 아무것도 할 수 없다는 과정을 설명합니다.

-

- 명령어 페치 과정이 실제로 Cortex-M에서 어떻게 진행되는지를 다룹니다. 특히 페치와 명령어 실행의 관계에 대해 설명하고 있습니다.

- 명령어 페치 과정이 실제로 Cortex-M에서 어떻게 진행되는지를 다룹니다. 특히 페치와 명령어 실행의 관계에 대해 설명하고 있습니다.

위 링크들을 참조하시면 질문하신 내용에 대한 보다 자세하고 유익한 정보를 얻으실 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

stm32cubeide 관련 문의

0

42

2

DMA 관련한 강의도 제작해주실 수 있으신가요 ?

0

90

1

그림들도 해석 할 수 있어야 하나요?

1

100

2

no-stlink

1

80

2

MAC으로 진행 질문드려요..

1

95

2

학습 진행 시, 사용하는 Board에 대한 문의 드립니다!

0

159

2

push pop 질문

1

190

2

STM32Fx Cortex ARM 프로그래밍 저자:홍봉조, 출판사:지식과 감성

0

242

1

CORTEX_02_ASSEMBLY 빌드시 에러

1

270

1

외부 ST Link 연결 이용한 SWD 방법

0

336

1

파이프라인과 명령어

1

326

1

명령어 fetch

0

238

1

lr 레지스터 LSB 값

1

258

1

Disassembly 창 문제

0

349

1

s702 강좌에서 사용한 technical reference manual 문서

1

323

1

s702에 원자적 Access 를 위한 BSRR 코드작성 부분에 대해서

1

270

1

s202 LED 점등 예제 실행시 에러

2

350

1

STM32F429I-DISC 보드의 펌웨어

2

394

1

제공되지 않은 강의교재

0

319

1

s524 테일체이닝 강의 질문

0

234

1

부트코드와 부트로더의 차이점

1

1524

1

메모리 맵 질문

0

278

1

xPSR 레지스터 플래그 값 및 기타 질문 드립니다.

1

858

2

컴퓨터 연결 및 회로도

0

420

1