파이프라인과 명령어

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

강사님, 안녕하세요! 아래의 내용은 강사님께서 다른 분의 질문에 답변 해주신 부분인데 이해가 안되서 질문 남깁니다.

(1)번을 처리하고 난 후, (2)(3)번을 한번에 페치하여 처리할 것을 짐작할 수 있겠죠. 그렇기에 (2)번 라인을 실행할 때는 페치를 건너뛸 것(쉬고 간다는 뜻)을 예상할 수 있을 겁니다.

(1)thumb2 명령어(32비트 명령어)

(2)thumb 명령어(16비트 명령어)

(3)thumb 명령어(16비트 명령어)

(4)thumb2 명령어(32비트 명령어)

cortex-m4에서 명령어 fetch 단위가 32bit인가요?

파이프라인 구조에서 1 clock마다 메모리에서 32bit를 fetch 하는 게 맞나요?

2-1. 이때 16bit thumb2 명령어 2개라면 각각의 명령어가 decode → execute가 진행되는건가요?

위 답변에서 (1)번 라인을 실행(즉, (2)번 라인을 decode))할 때 페치를 건너 뛰는게 아닌가요?

답변 부탁드립니다.

답변 1

1

안녕하세요. 박정원님!

32비트 메모리 버스 대역폭을 충분히 활용할 수 있도록 페치(FETCH) 동작은 32비트로 하도록 설계되어 있습니다. 명령어가 fetch된 후, 디코더는 명령어 스트림을 분석하여 현재 명령어가 16비트인지 32비트인지를 결정합니다. 만약 16비트 명령어라면, 32비트 fetch 결과에서 다음 16비트 명령어로 이동할 수 있습니다. 32비트 명령어인 경우에는 다음 명령어 fetch로 넘어갑니다, 또한 16비트 Thumb 명령어의 경우, 한 번의 fetch로 두 개의 명령어를 가져올 수 있으며, 이후 각 명령어는 디코드와 실행 과정을 거치게 됩니다. 하지만, 실행은 단위 명령 크기로 할 수 밖에 없기에 해당 명령어가 16비트 THUMB 명령어도 1클럭이 소모되며, 32비트 THUMB-2 명령어의 경우도 1클럭이 소모 되겠습니다.

마무리. 이러한 방식으로 Cortex-M4는 명령어 길이에 따라 동적으로 fetch, decode, execute 과정을 조절하여, 프로세서의 성능과 효율성을 최적화합니다

0

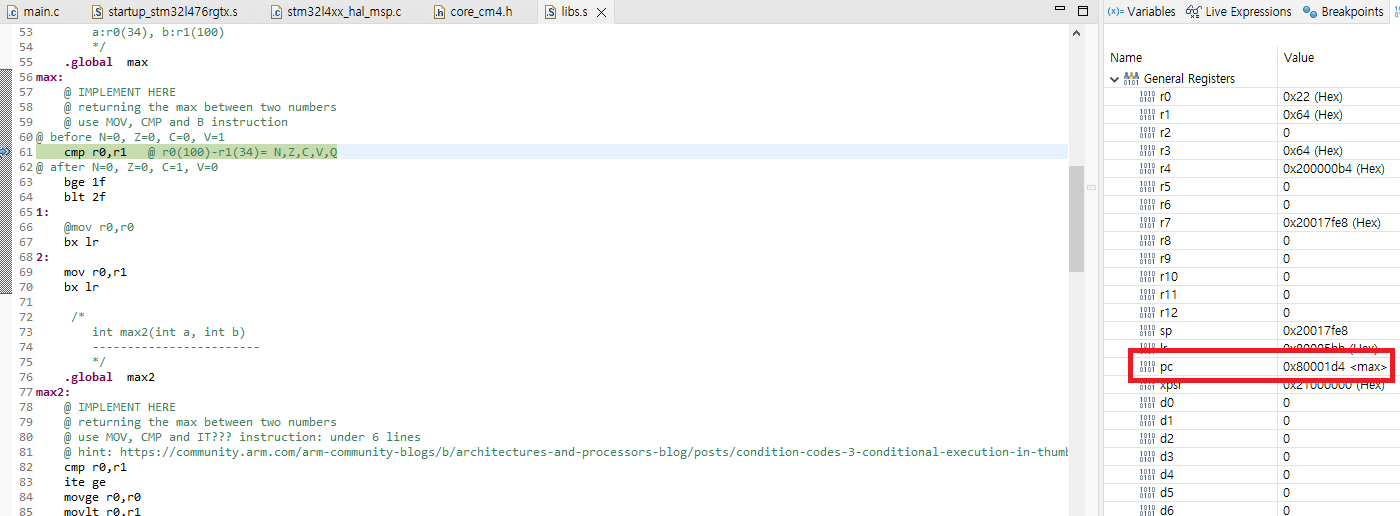

강사님, 제가 stm32cubeide로 예제를 실습하는데 pc register가 +4가 아닌 +2가 되는데... 이 경우는 어떻게 설명될 수 있을까요?

PC 0x80001d4

PC 0x80001d4

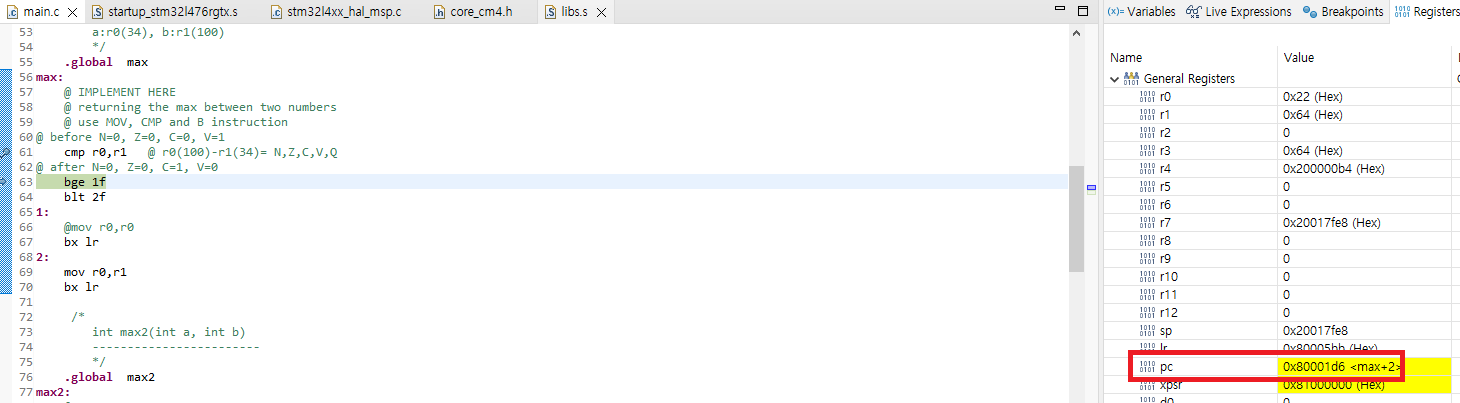

PC 0x80001d6

PC 0x80001d6

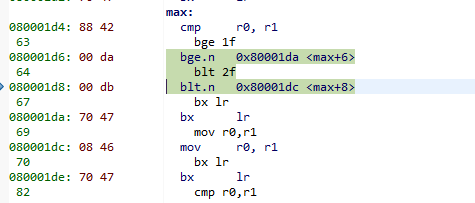

Disassembly 창입니다.

Disassembly 창입니다.

현재 저한테 NUCLEO-L476RG가 있어 이걸로 실습 중입니다

1

Thumb-2 명령어 세트를 사용하는 Cortex-M3는 16비트와 32비트 명령어를 모두 지원합니다. 프로세서는 먼저 16비트(2바이트) 단위로 명령어를 해석을 시도합니다. 만약 해당 명령어가 16비트로 완전히 해석되면 PC는 +2 증가합니다. 그러나 이는 실행 후의 동작으로, 페치 자체는 여전히 4바이트를 기반으로 이루어집니다.

만약 처음 16비트를 해석한 결과 해당 명령어가 32비트 명령어의 일부임이 확인되면, 프로세서는 추가적으로 다음 16비트를 결합하여 전체 32비트 명령어를 형성하고, 이 경우 PC는 +4 증가합니다.

따라서, 페치 동작은 항상 4바이트 단위로 이루어지지만, PC의 증가량은 실행 중인 명령어가 16비트인지 32비트인지에 따라 다르게 나타날 수 있습니다. 이는 명령어의 길이가 다르기 때문이며, 페치된 명령어 블록에서 필요한 만큼의 데이터만을 사용하여 명령어를 실행합니다.

이로 인해 페치 과정과 PC의 증가 사이에는 직접적인 연관이 있으나, 명령어의 길이에 따라 PC의 증가량이 달라질 수 있습니다. 이는 프로세서가 높은 실행 효율과 메모리 접근 최적화를 동시에 달성할 수 있게 해주는 중요한 설계 특징입니다.

stm32cubeide 관련 문의

0

46

2

DMA 관련한 강의도 제작해주실 수 있으신가요 ?

0

95

1

그림들도 해석 할 수 있어야 하나요?

1

100

2

no-stlink

1

80

2

4개의 CPU 사이클이 필요한 이유

1

100

2

MAC으로 진행 질문드려요..

1

95

2

학습 진행 시, 사용하는 Board에 대한 문의 드립니다!

0

159

2

push pop 질문

1

190

2

STM32Fx Cortex ARM 프로그래밍 저자:홍봉조, 출판사:지식과 감성

0

242

1

CORTEX_02_ASSEMBLY 빌드시 에러

1

270

1

외부 ST Link 연결 이용한 SWD 방법

0

339

1

명령어 fetch

0

238

1

lr 레지스터 LSB 값

1

258

1

Disassembly 창 문제

0

349

1

s702 강좌에서 사용한 technical reference manual 문서

1

325

1

s702에 원자적 Access 를 위한 BSRR 코드작성 부분에 대해서

1

271

1

s202 LED 점등 예제 실행시 에러

2

351

1

STM32F429I-DISC 보드의 펌웨어

2

394

1

제공되지 않은 강의교재

0

319

1

s524 테일체이닝 강의 질문

0

234

1

부트코드와 부트로더의 차이점

1

1525

1

메모리 맵 질문

0

280

1

xPSR 레지스터 플래그 값 및 기타 질문 드립니다.

1

862

2

컴퓨터 연결 및 회로도

0

421

1