인프런 커뮤니티 질문&답변

d_ff_test.v 질문있습니다!

작성

·

326

1

- 강의 내용외의 개인 질문은 받지 않아요. (개인 과제, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

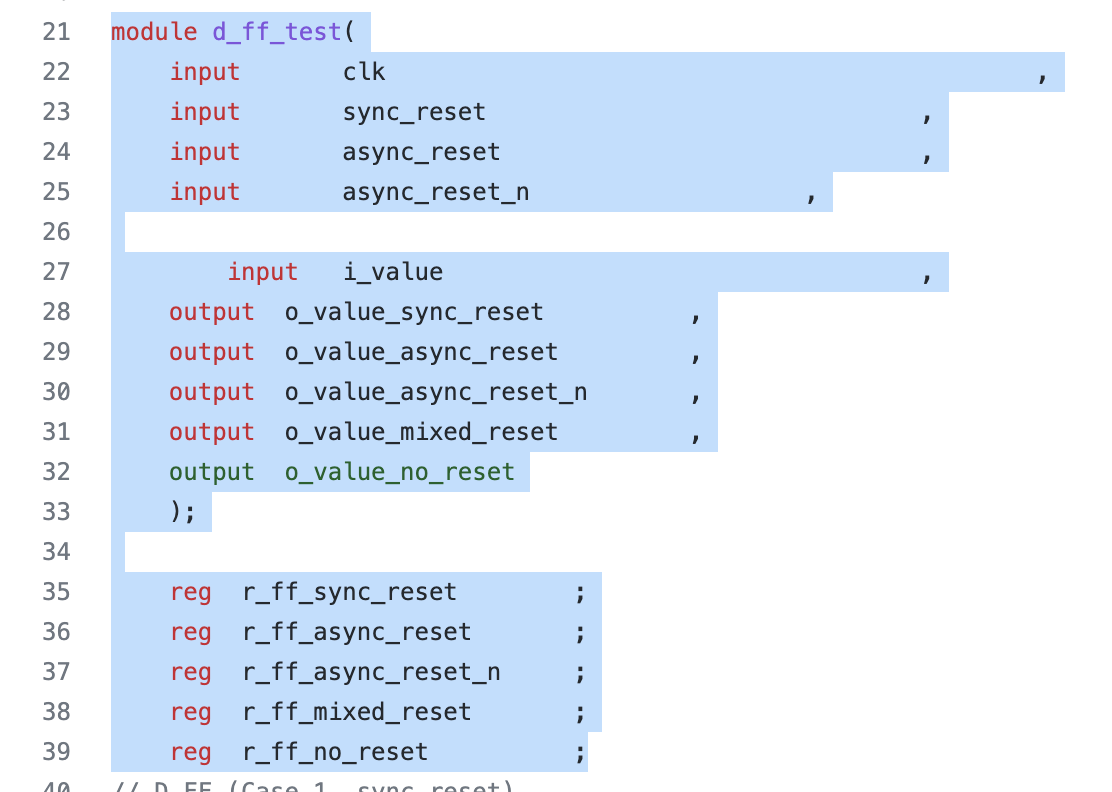

stimulus 블럭 코드들은 전부 이해가 가고, dut input output 포트까지도 이해했습니다.

다만 r_ff_~~~ 들이 어떤 신호인지 영상을 계속 돌려보아도 모르겠습니다 ㅠㅠ 마지막에 출력에 assign되는걸 보면 확실히 출력은 맞는것같은데

always문에서 바로 o_value~에 값을 넣어주지 않고 r_ff에 넣어준후 assign하는 이유는 무엇인가요?

답변 2

1

output의 external에 해당하는 o_value(wire)를 꼭 따로 선언하지않아도 됨. (wire형의 external을 별도 선언하는것에 얽메이지 말고 생략해도 된다.)

syntax 이기에 가능

internal에 해당하는 reg형(reg or wire사용가능하지만 reg사용한)의 r_ff를 internal과 동시에 external로 사용하여 waveform에서 확인해도 문제는 없음. 그래서 최종 아웃이 reg or wire 둘다 가능한것임.

syntax 이기에 가능

(꼭 별도 선언으로 internal > external의 flow 를 지키지 않아도 된다. 즉 output의 internal==external이기때문에 external을 별도 선언해서 꼭 wire로 assign해야한다는것은 잘못된 지식. external 생략후 reg로 내보내도 문제될게없음.)

syntax 이기에 가능

하지만 본 예제에서는 맛비님이 선호하는 코딩 스타일이 적용된 것으로 reg, wire을 각각 따로 선언해 output의 internal, external로 사용한것임

syntax 이기에 가능

결론은 최종 waveform에 나오는 신호를 꼭 wire로 맞춰줄 필요가 없다. reg or wire가 사용 가능한 internal 선에서 끝내도 된다.

syntax 이기에 가능

네 전부 확인했어요 :)

1

안녕하세요 :)

Verilog 문법에 관련되 질문같아요.

문법을 공부하시면 자연스럽게 해결이 되실 것 같아요 :) (문법책 1독 추천드려요)

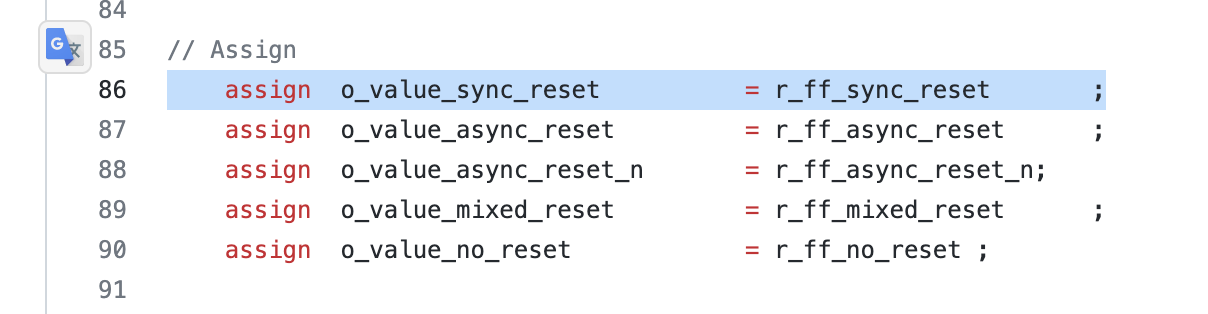

o_value 는 wire 입니다.

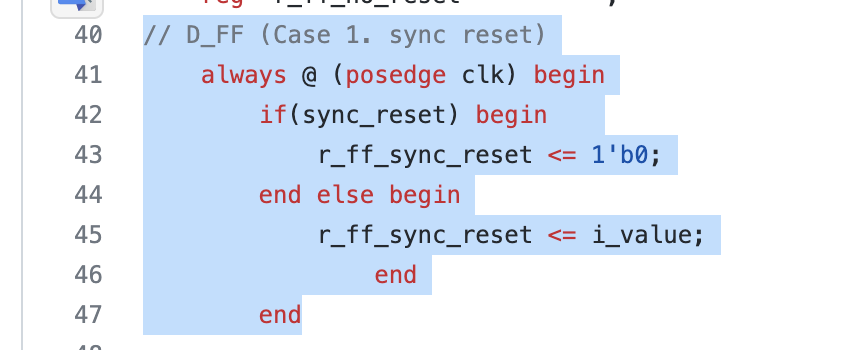

r_ff 는 reg type 이고 always @ (posedge clk) begin 에 의해 F/F 입니다.

wire 에 assign 을 사용했습니다. (이정도면.. 이유는 충분하긴한데..)

즐공하세요 :)

o_value(dut에서 나간 후 출력신호)는 testbench 입력에따라 continuously driving되기때문에 wire를 사용해야함.

하지만 f/f 기능 구현을 위해 (값을 일정시간 유지해야하므로, dut에서 나가기 전 값을 저장하기 위해) reg를 사용해야해서 r_ff를 reg로 따로 선언.

정리하면 "dut에서 나간 출력(o_value)은 이전 값에 따라 계속 변하기 때문에 wire를 사용해야하지만, f/f특성상 dut에서 나가기 전 값(r_ff) 저장 위해 reg를 사용해야하므로 따로 선언해준것"

제가 이해한게 맞을까요?

음........

o_value(dut에서 나간 후 출력신호)는 testbench 입력에따라 continuously driving되기때문에 wire를 사용해야함.

여기서 "testbench 입력에따라" 라는 말은 없어야 자연스러울 것 같아요. (무관하니까요)

HDL 은 회로를 만드는 언어입니다. 이점을 유의하시면 좋을 것 같아요.

정리하면 "dut에서 나간 출력(o_value)은 이전 값에 따라 계속 변하기 때문에 wire를 사용해야하지만, f/f특성상 dut에서 나가기 전 값(r_ff) 저장 위해 reg를 사용해야하므로 따로 선언해준것"

제가 이해한게 맞을까요?

적으신 말에서 "때문에" 가 뭔가 저의 마음을 싱숭생숭하게 하는데요.

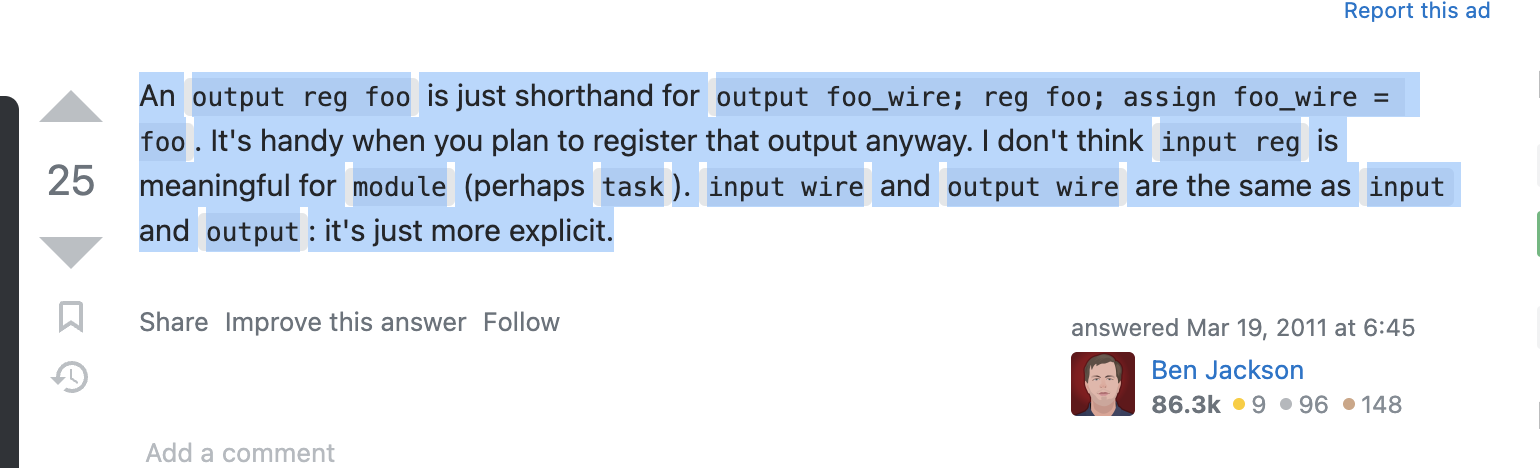

문법적으로 추가 설명 해드릴께요. o_value 가 wire 가 아닌 reg 가 되어도 되기 때문입니다. (wire 를 강제할 필요가 없어요)

o_value 의 출력값 == r_ff 의 출력값 같습니다. 제 코딩 스타일이 Port 는 wire 로 사용하는 것을 좋아해서, o_value 를 wire 로 선언했어요.

output reg o_value_sync_reset; // 이렇게 선언하고 port 는 output 이면서 reg

r_ff_sync_reset 을 o_value_sync_reset 으로 변경하시고

마지막 assign 문을 지워도 동일한 결과가 나와요.

마지막 assign 문을 지워도 동일한 결과가 나와요.

다시 정리해보시겠어요?

https://stackoverflow.com/questions/5360508/using-wire-or-reg-with-input-or-output-in-verilog

정리하면 "dut에서 나간 출력(o_value)은 이전 값에 따라 계속 변하기 때문에 wire를 사용해야하지만, f/f특성상 dut에서 나가기 전 값(r_ff) 저장 위해 reg를 사용해야하므로 따로 선언해준것"

문맥은 전혀 문제가 없습니다. 좋아요.

위에 답변을 적은건 코딩스타일 (== 문법) 때문이고요.

이 말이 맞게 되는 코딩스타일이 되려면,

`default_nettype none

을 강제로 .v 내에 추가하시면 옳은 문장이 되실꺼에요.

즐공하세요 :)

wire, reg가 정말 헷갈리네요 ㅠㅠ 책을 주문했는데 아직 안 와서 유튜브 vhdl 문법 강의에서 알려준 내용에만 의존하다보니 더 헷갈리는것같습니다.

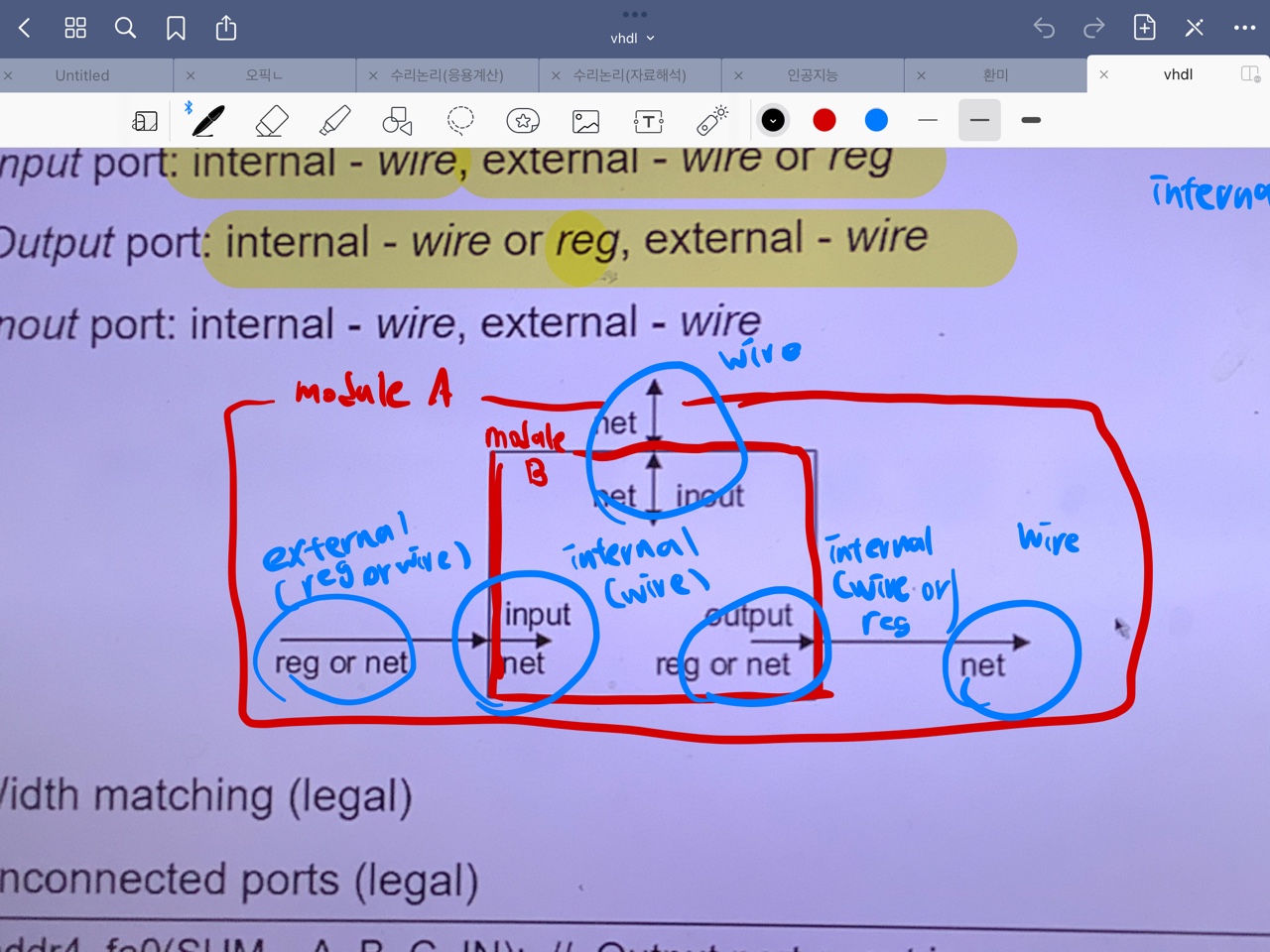

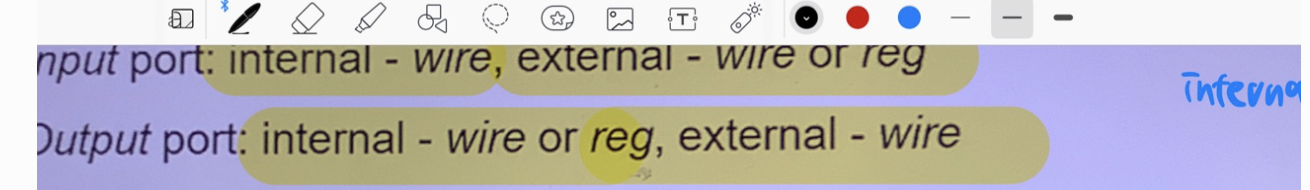

사진에서 moduleA(tb_d_ff.v)쪽에서 moduleB(d_ff_test.v)로 가는 external A(reg or wire)가 tb_d_ff에서의 reg형 신호들(clk,clk_enable...등)

module B(d_ff_test.v)로 들어온 internal B(wire)가 d_ff_test의 input들,

module B(d_ff_test.v)에서 moduleA(tb_d_ff.v)로 나가기 전 internal B(reg or wire)가 d_ff_test의 reg형 r_ff신호,

최종적으로 다시 테스트벤치쪽으로 나온 맨오른쪽 external A(wire)가 assign한 o_value 라고 이해했는데 o_value에서 reg를 사용해도 된다는 것은 몰랐던 부분이네요... 책이 도착하면 syntax부터 다시 봐야겠습니다...

책을 주문했지만, 아직 도착하지 않아서 유튜브로 본 verilog hdl 문법 강의 내 자료에만 의존하다보니 syntax 질문으로 맛비님을 너무 성가시게 하는 것은 아닌지 죄송스럽네요... 죄송하고 감사합니다...

적어주신 문장은 보고계신 자료를 통해서 이해하시면 좋을 것 같아요. (보는 저도 헷갈리는..ㅠㅠ)

=====================================

그림 보시면 output 은 reg 가 될 수 있다는것이 있네요. (이게 왜? 를 이해하시려다 보니.. 헷갈림의 단계에 오신 것 같아요) 왜? 도 중요하지만, IEEE 가 정한 Verilog 문법이 이래요. (이게 정답인데..)

그림 보시면 output 은 reg 가 될 수 있다는것이 있네요. (이게 왜? 를 이해하시려다 보니.. 헷갈림의 단계에 오신 것 같아요) 왜? 도 중요하지만, IEEE 가 정한 Verilog 문법이 이래요. (이게 정답인데..)

Syntax 만 해결하시면 될 것 같은데, 책을 보시는 것을 꼭 추천드려요.

혼란만 가중이 되실듯..하고 많이 해보시면 자연스러워지실꺼에요.

즐공하세요 :)

internal external에서 이해에 어려움이 있는데 정말 마지막으로 이해를 시도하고, 안된다면 책 올때까지 그냥 다음강의로 넘어가려합니다. 최대한 간추려보았습니다. (어제부터 이해를 시도한 주제라서ㅠㅠ 성격상 하나에서 막히면 다음으로 잘 넘어가지를 못합니다... 죄송합니다)

결국 값 측면에서 보면 r_ff==o_value 임. (internal인 r_ff와 external인 o_value는 같음)

그래서

output의 external에 해당하는 o_value(wire)를 꼭 따로 선언하지않아도 됨. (wire형의 external을 별도 선언하는것에 얽메이지 말고 생략해도 된다.)

internal에 해당하는 reg형(reg or wire사용가능하지만 reg사용한)의 r_ff를 internal과 동시에 external로 사용하여 waveform에서 확인해도 문제는 없음. 그래서 최종 아웃이 reg or wire 둘다 가능한것임.

(꼭 별도 선언으로 internal > external의 flow 를 지키지 않아도 된다. 즉 output의 internal==external이기때문에 external을 별도 선언해서 꼭 wire로 assign해야한다는것은 잘못된 지식. external 생략후 reg로 내보내도 문제될게없음.)

하지만 본 예제에서는 맛비님이 선호하는 코딩 스타일이 적용된 것으로 reg, wire을 각각 따로 선언해 output의 internal, external로 사용한것임

결론은 최종 waveform에 나오는 신호를 꼭 wire로 맞춰줄 필요가 없다. reg or wire가 사용 가능한 internal 선에서 끝내도 된다.

업무중에 바쁘실텐데 가볍게 한번 읽어보시고 맞다면 하트만 남겨주셔도 됩니다!! 아니라면 "책"이라고 한글자만 남겨주시면 이 질문을 마지막으로 다음 강의로 스킵하고 책오면 혼자 해결해보겠습니다!!!

정말 감사합니다!!!!!!!!!!! 속이 후련하네요 ㅎㅎㅎㅎㅎㅎ 열공하겠습니다!!!!