인프런 커뮤니티 질문&답변

fsm 모듈에서 case문 문법 관련 질문드립니다.

작성

·

311

1

안녕하세요 맛비님. 강의 열심히 듣고 있는 수강생입니다. ㅎㅎ

fsm 실습편과 응용실습편을 다 보고 난 뒤 맛비님이 응용실습편에서 코드 수정하신 부분을 보고 궁금증이 생겨 질문드립니다.

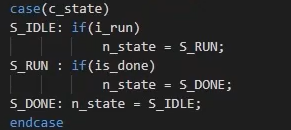

응용실습편에서, 위 사진의 코드에서 c_state =S_RUN일 때 is_done=0인 경우를 고려해 else n_state = S_RUN; 코드를 추가한 것으로 이해했습니다.

그렇다면 같은 이유로, c_state = S_IDLE 일 때 else n_state = S_IDLE; 코드를 추가해 주어야 하지 않을까요??

답변 1

1

설계독학맛비

지식공유자

안녕하세요 :)

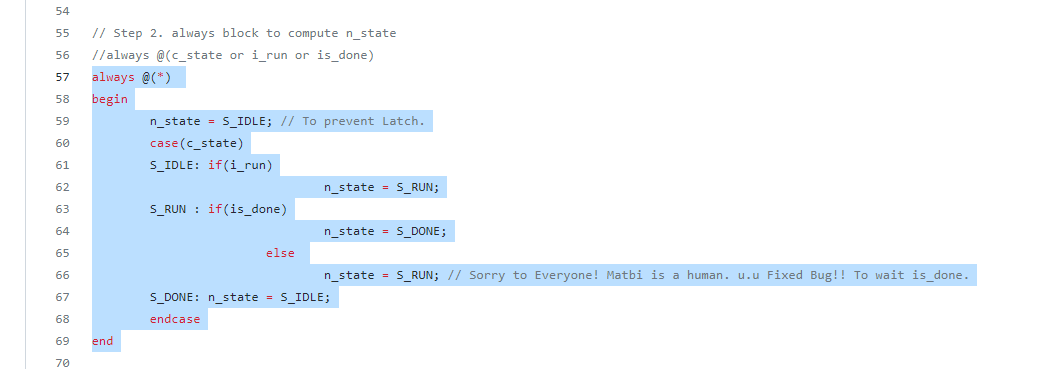

실습응용편 17장 실습코드 59번째 line 을 보시면, default 가 S_IDLE 입니다.

그렇다면 같은 이유로, c_state = S_IDLE 일 때 else n_state = S_IDLE; 코드를 추가해 주어야 하지 않을까요??

없어도 괜찮습니다. (물론 질문하신 내용을 추가해도, 현 코드에서는 function 적으로 match 문제없어요.)

즐공하세요 :)

설계독학맛비

지식공유자

지우고 돌려보셔서 확인해보셔도 될 것 같아요:)

57~69 번째 라인은 combinational logic 이고, full case 가 되어야 latch 가 발생하지 않습니다. 59번째 line 에 의하여 latch 는 발생하지 않습니다. 59번째 라인이 default 의 역할을 하고 있어요.

질문주신 내용의 답은

59번째 라인으로 인하여, IDLE 이됩니다.

한 가지 더 여쭤봐도 될까요? 너무 간단한 질문일까 죄송스럽네요 ㅠㅠ

올려주신 사진에서 65,66번째 코드가 없다면 is_done =0일 때 c_state는 x(정해지지 않음)으로 처리되는 걸까요?