인프런 커뮤니티 질문&답변

schemetic 질문드립니다.

작성

·

287

2

안녕하세요 맛비님

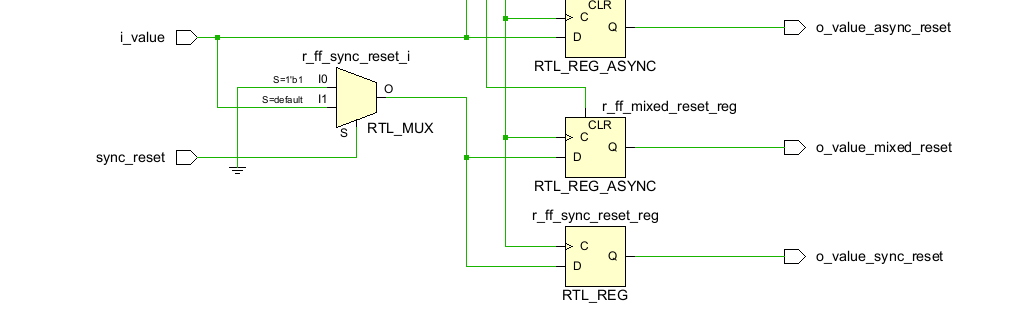

맛비님께서 올리신 DUT를 schemetic하였을 때 다음과 같은 사진이 나옵니다.

사진을 보시면 MUX 부분이 있는데,

MUX에 S에 0이 들어가면 O로 I0이 나오고,

S에 1이 들어가면 O로 I1이 나오는 것으로 알고 있습니다.

그렇다고 하면, 다음 사진을 볼 때,

sync_reset이 1일 때, i_value가 sync_reset D F/F에 들어가는데, 0이 들어가야하지 않나요??

읽어주셔서 감사합니다.

- 강의 내용외의 개인 질문은 받지 않아요. (개인 과제, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

네 맛비님.

코드는 다음과 같습니다. 코드상으로는,

sync_reset이 1이면 r_ff_sync_reset (D F/F) 의 입력이 0입니다.

sync_reset이 0이면 r_ff_sync_reset (D F/F) 의 입력이 i_value입니다.

그런데, 위를 보면, sync_reset이 RTL_MUX의 S로 들어가고,

(제가 아는 지식으로는) S에 0이 들어가면 MUX의 출력이 I0, 1이 들어가면 MUX의 출력이 I1으로 알고있습니다.

이 논리대로라면,

MUX의 S인 sync_reset이 1이 들어가면 I1인 i_value가 r_ff_sync_reset (D F/F) 입력으로 들어갑니다.

하지만, 코드상으로는 sync_reset이 1이면, 0이 r_ff_sync_reset (D F/F) 입력으로 들어가야합니다.

코드와 schemetic의 해석이 왜 다른건지 궁금합니다.