인프런 커뮤니티 질문&답변

always @(*) 와 관련하여..

작성

·

696

1

안녕하세요, 좋은 강의 해 주셔서 잘 듣고 있습니다.

FSM 실습 예제에서 한가지 궁금한 부분이 생겼습니다.

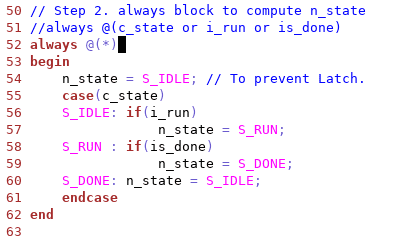

fsm_test.v 의 52번 줄에 있는,

always @(*)

에서 *가 내부 변수중 하나라도 변화를 하면 동작하게 된다고 하셨는데, 내부 변수가 52번줄 ~ 62번 줄 사이에 있는 always begin~end 안에 기술된 reg타입으로 선언된 c_state 와 n_state만을 이야기하는 것인지요?

제가 asterisk 에 대한 개념이 'everything' 을 의미한다는 어떤 고정관념을 가지고 있어서 그런지, 변하고 있는건 clk도, reset_n 도 변하고 있는데 그 변화에도 반응을 하지 않을까 라는 생각이 들었습니다.

질문 작성하면서 영상 아래의 질답 내용에 verilog 2001 문법에 대한 언급이 있어 찾아보았더니 'Simulation and synthesis will automatically be sensitive to all signals read within the procedure. @* was added in Verilog-2001.' 란 내용이 있는데, 봐도 여전히 명확히 이해되지가 않았습니다.^^;

all signals read within the procedure 의 범위가 module 전체 안에서인지, 혹은 always @ begin ~ end 까지를 의미하는 것인지 궁금합니다.

퀴즈

하드웨어 설계에서 FSM(Finite State Machine)의 주요 목적은 무엇일까요?

데이터 저장 용량 최대화

제어 로직을 체계적으로 설계

클럭 주파수 자동 조정

전력 소모량 실시간 측정

답변 1

1

안녕하세요 :) 좋은질문같아요.

fsm_test.v 의 52번 줄에 있는,

always @(*)

에서 *가 내부 변수중 하나라도 변화를 하면 동작하게 된다고 하셨는데, 내부 변수가 52번줄 ~ 62번 줄 사이에 있는 always begin~end 안에 기술된 reg타입으로 선언된 c_state 와 n_state만을 이야기하는 것인지요?

해당 문법은 combinational logic 임으로, input 이 변경되면 바로 output 이 반영됩니다. 즉, always @(*) 내부의 모든 변수라고 생각하시면 됩니다. (i_run, i_done 도 포함시켜야 합니다.)

HDL 은 HW 를 만드는 언어입니다.

always 내부에 없는 변수에 값이 흔들린다는 뜻은, 회로적으로 always 내부에 없는 변수에 연결이 되어있다는 뜻으로 해석됩니다. 이는 오류입니다.

always @ begin ~ end

내부의 변수 입니다.

즐공하세요 :)