인프런 커뮤니티 질문&답변

Counter 설계 관련 질문2

해결된 질문

작성

·

433

1

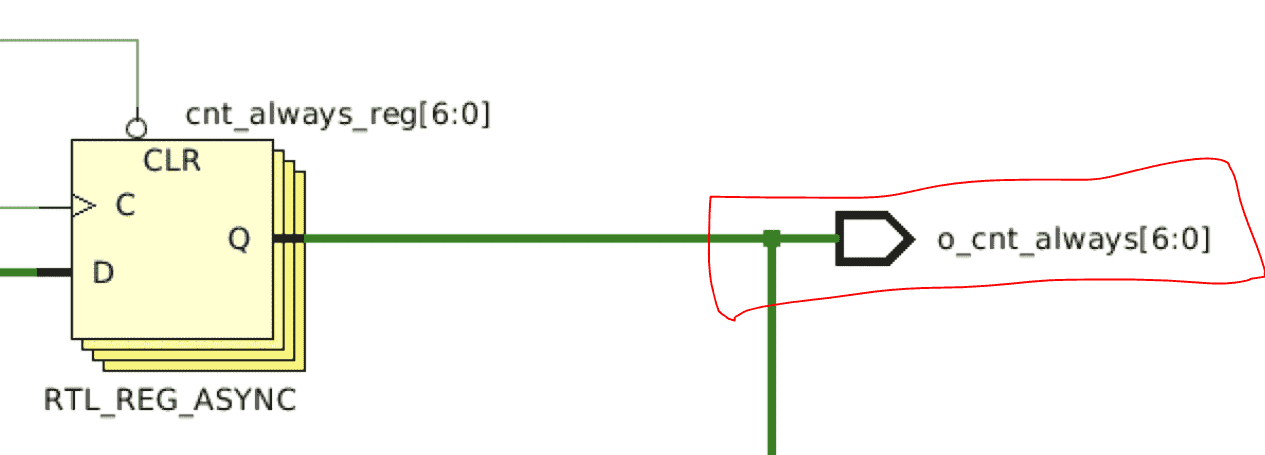

1. 제가 RTL analysis를 보면서 궁금했던 점은 verilog 코드상에서

reg [6:0] cnt_always; 라고 선언하면 7bit 짜리 reg가 1개 생기는 것으로 알고 있었습니다

하지만 그림을 보면 마치 1bit짜리 register를 7개 쌓아놓은 것처럼 합성이 된거 같은데 제 이해가 맞는지 궁금합니다

만약 제 생각대로 1bit 짜리 register 7개 쌓아놓은 것으로 합성이 된거라면

reg cnt_always [6:0] 과 다를것이 없지 않나요? 왼쪽 문법도 1bit짜리 7개가 있다는 점에서는 동일하지 않은가요?

2. 제가 입출력 포트에 대한 이해가 부족했던 것 같습니다. 모듈에서 입출력 포트라고 하면 뭔가가 있을거라고 생각을 했습니다.

하지만 RTL 그림을 보니 입출력 포트라는게 현실세계에 대입해 생각해보면 단순한 입출력 단자다...

usb 포트 연결하듯이 데이터가 들어가는 구멍이다 이렇게 생각이 들었습니다

맞는 생각인가요?

3. output reg o_cnt_always 로 선언한다면 합성이 어떻게 되는 것인가요? 출력포트 즉 출력 단자가 값을 저장한다???

굉장히 이상하게 느껴집니다

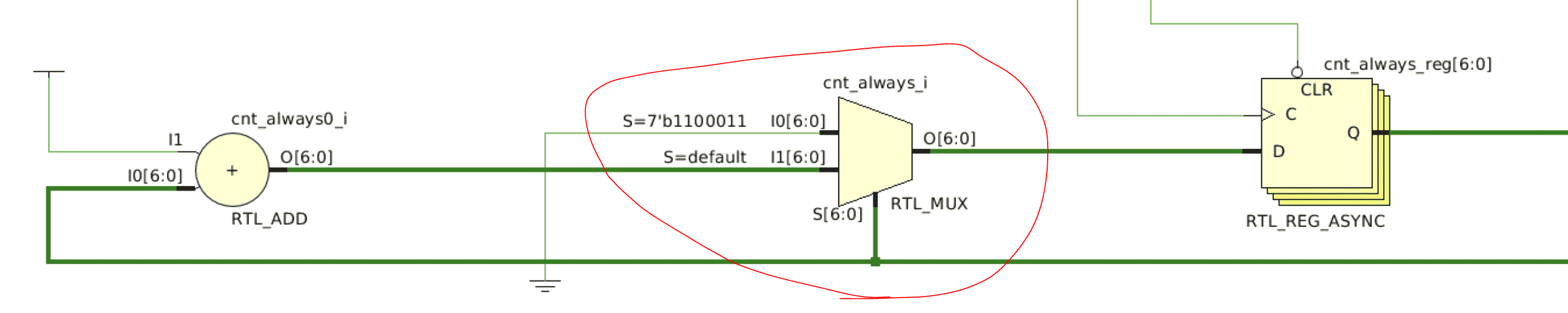

4. RTL 그림을 보다 보니 제가 기술하지 않은 MUX가 들어가 있던데, 이건 Tool 이 합성하면서 제가 작성한 코드의 로직이 HW적으로 돌아갈 수 있게 알아서 집어 넣어 준 것인가요??

MUX 기능을 생각해 보면 if - else 문을 MUX로 구현해 준 것 같다는 생각이 듭니다. 이 생각이 맞는지 궁금합니다.

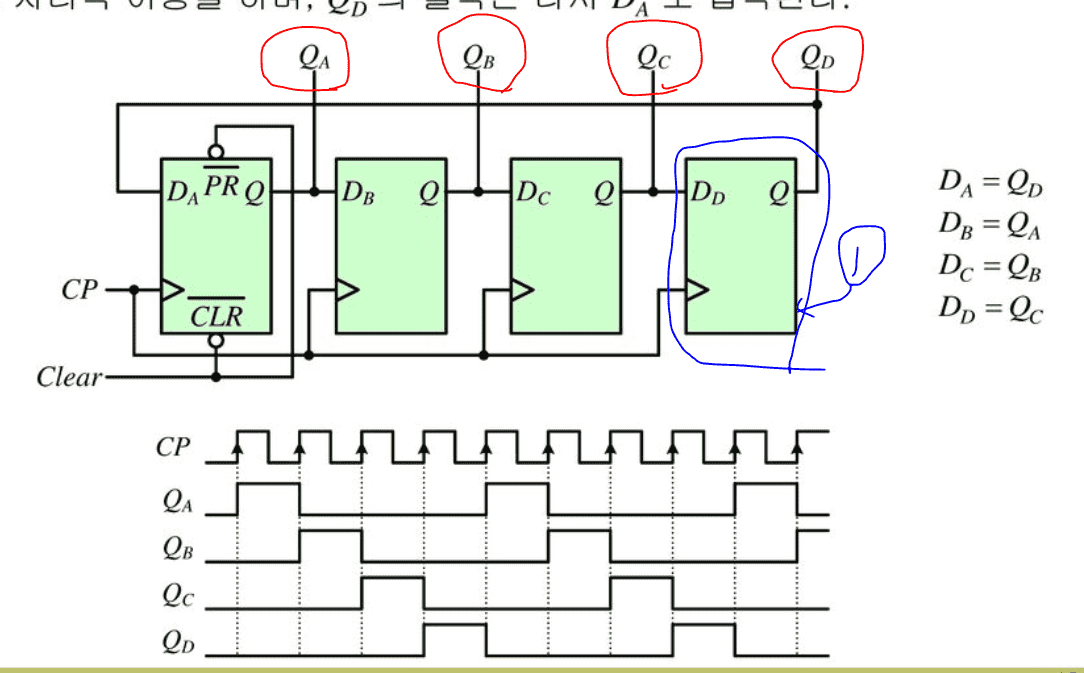

5. 제가 생각한 카운터는 아래 사진과 같습니다. 제가 학교에서 배울 때는 D ff 을 별도의 모듈로 만든 후에(파란색 1번 모듈을 d_ff.v 로 따로 만들었습니다) 이 모듈(d_ff.v)을 counter.v라는 파일에 include 해서 아래 사진과 같이 여러개의 D ff를 연결해서 카운터로 만들었었습니다. 맛비님 코드는 제가 배운 방식처럼 선이 여러개(아래 사진에서 QA QB QC QD) 나오는 것이 아니라 그냥 선이 하나만(o_cnt_always) 나오는데 둘 사이의 차이점이 뭔가요???

답변 1

1

안녕하세요 :)

하나씩 적어보겠습니다.

1. 제가 RTL analysis를 보면서 궁금했던 점은 verilog 코드상에서

reg [6:0] cnt_always; 라고 선언하면 7bit 짜리 reg가 1개 생기는 것으로 알고 있었습니다

하지만 그림을 보면 마치 1bit짜리 register를 7개 쌓아놓은 것처럼 합성이 된거 같은데 제 이해가 맞는지 궁금합니다

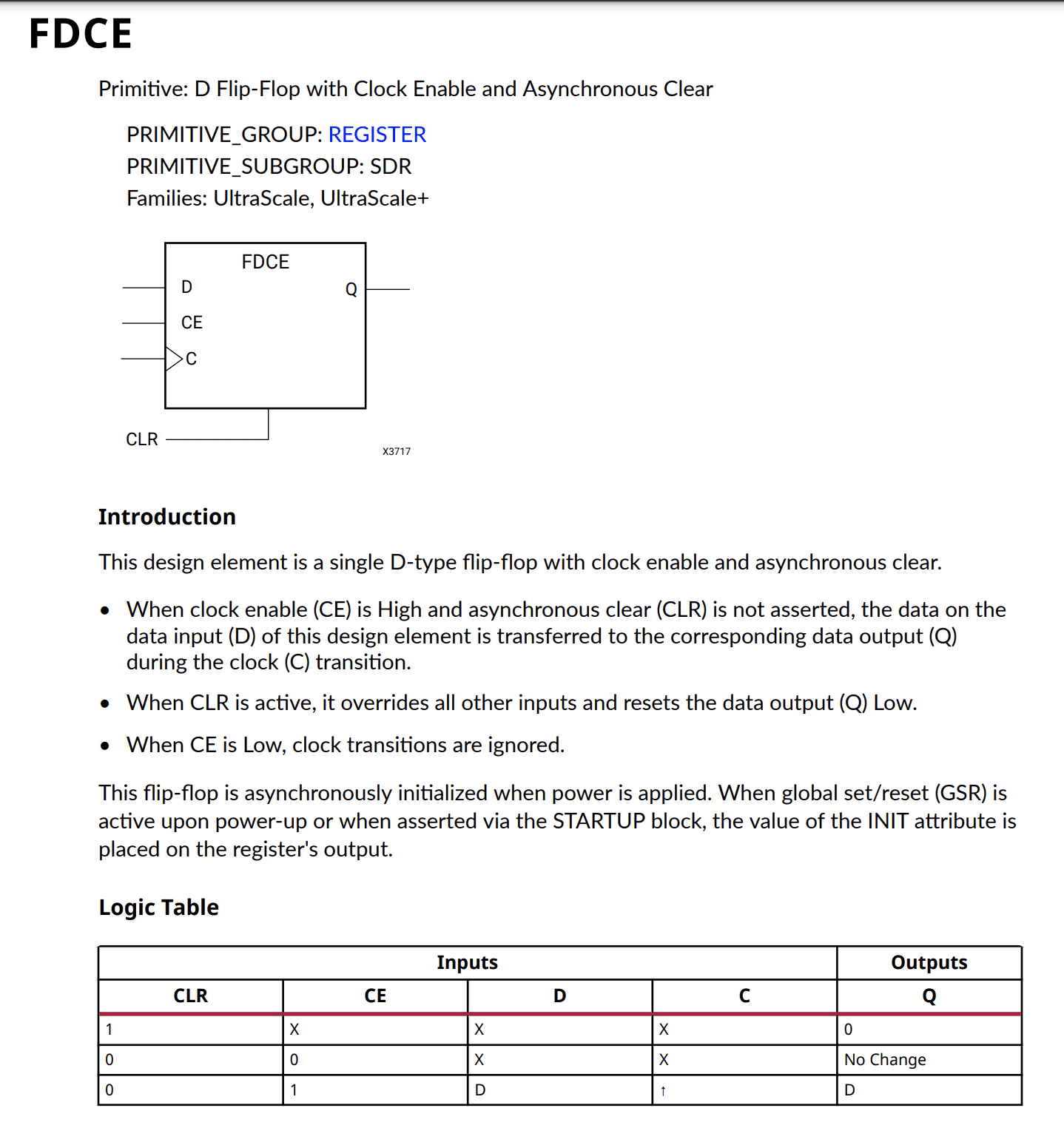

F/F 의 Primitive cell 의 문서를 보시면 해결이 되실 겁니다. 1bit 맞다.

https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_2/ug974-vivado-ultrascale-libraries.pdf

만약 제 생각대로 1bit 짜리 register 7개 쌓아놓은 것으로 합성이 된거라면

reg cnt_always [6:0] 과 다를것이 없지 않나요? 왼쪽 문법도 1bit짜리 7개가 있다는 점에서는 동일하지 않은가요?

질문을 이해하지 못했습니다. (뭐랑 뭐가 다른거죠?)

2. 제가 입출력 포트에 대한 이해가 부족했던 것 같습니다. 모듈에서 입출력 포트라고 하면 뭔가가 있을거라고 생각을 했습니다.

하지만 RTL 그림을 보니 입출력 포트라는게 현실세계에 대입해 생각해보면 단순한 입출력 단자다...

usb 포트 연결하듯이 데이터가 들어가는 구멍이다 이렇게 생각이 들었습니다. 맞는 생각인가요?

음... 뭐.... "현실세계 -> 모듈관점" 으로 치환하면 맞는 생각인 것 같아요. 다음 링크 참고

https://www.hdlworks.com/hdl_corner/verilog_ref/items/PortDeclaration.htm

3. output reg o_cnt_always 로 선언한다면 합성이 어떻게 되는 것인가요? 출력포트 즉 출력 단자가 값을 저장한다???

굉장히 이상하게 느껴집니다

output reg o_cnt_always;

다음 문구와 동일하죠. 2 line 을 1 line 으로 적은 문법일 뿐입니다.

output o_cnt_always;

reg o_cnt_always;

syntax 에 집중하기 보다는, 만들어질 회로에 집중하시면... 전혀 이상할 것이.. 없는데 (저는 굉장히 정상적으로 느껴지는데.. (어디가 굉장히 이상하죠..?;;;;;)

4. RTL 그림을 보다 보니 제가 기술하지 않은 MUX가 들어가 있던데, 이건 Tool 이 합성하면서 제가 작성한 코드의 로직이 HW적으로 돌아갈 수 있게 알아서 집어 넣어 준 것인가요??

Yes

MUX 기능을 생각해 보면 if - else 문을 MUX로 구현해 준 것 같다는 생각이 듭니다. 이 생각이 맞는지 궁금합니다.

Yes

5. 제가 생각한 카운터는 아래 사진과 같습니다. 제가 학교에서 배울 때는 D ff 을 별도의 모듈로 만든 후에(파란색 1번 모듈을 d_ff.v 로 따로 만들었습니다) 이 모듈(d_ff.v)을 counter.v라는 파일에 include 해서 아래 사진과 같이 여러개의 D ff를 연결해서 카운터로 만들었었습니다. 맛비님 코드는 제가 배운 방식처럼 선이 여러개(아래 사진에서 QA QB QC QD) 나오는 것이 아니라 그냥 선이 하나만(o_cnt_always) 나오는데 둘 사이의 차이점이 뭔가요???

추상화의 Level 입니다. 라고 답변드릴께요. 제 눈에는 올려주신 그림으로는 답이 안됩니다.

일단 올려주신건 Counter 가 아니니까요. (교수님한테 물어보심이...?)

다음 질문 기다리겠습니다! 가즈아~~ :)

상세한 답변 감사합니다!