Verilog를 이용한 FPGA 활용기초 37p 질문입니다.

75

작성한 질문수 4

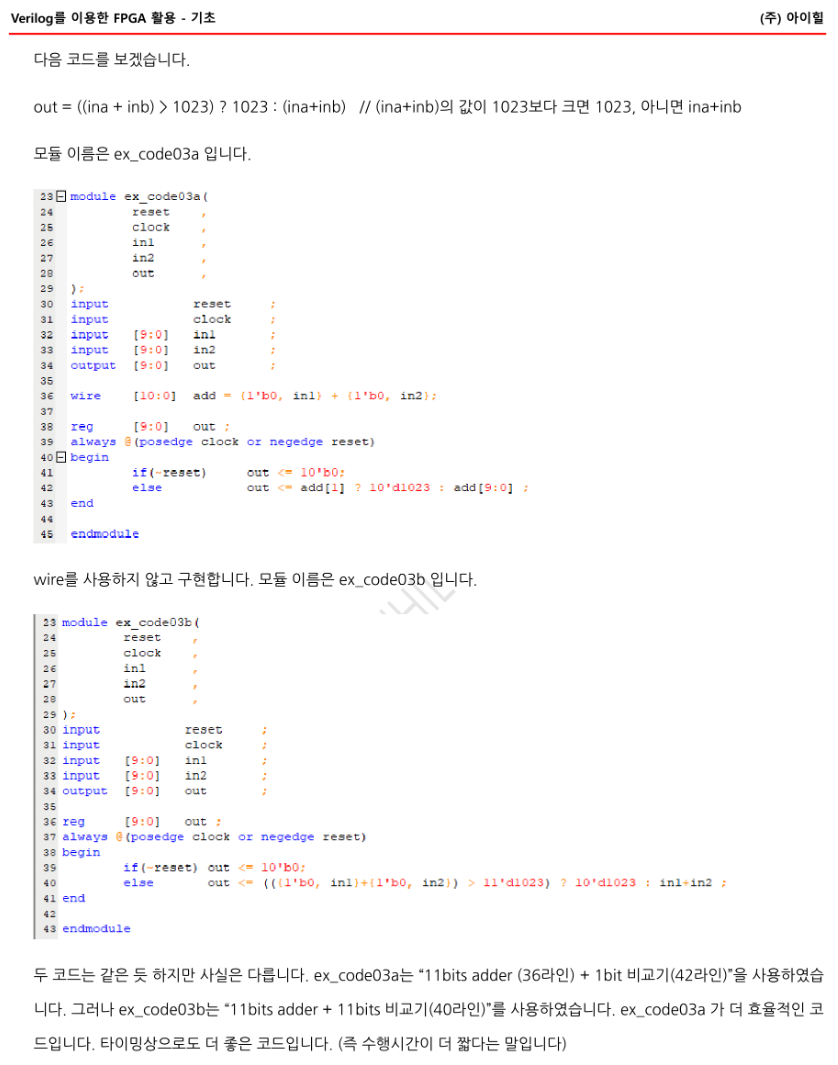

안녕하세요. 덧셈을 하는 방식에 따라 어떤 것이 더 효율적인지 말씀해주셨습니다. 37page 설명에서는 ex_code3a가 더 효율적인 코드라고 명시되어 있는데 그 이유를 궁금합니다!

답변 2

1

안녕하세요?

ex_code03a 는 11bits adder + 1bits 비교기를 사용하고,

ex_code03b는 11bits adder + 11bits 비교기를 사용하기 때문에 ex_code03a가 더 효율적인 코드입니다.

ex_code03a의 42라인에 오타가 있네요 ㅠㅠ 아래와 같이 수정해야 합니다.

out <= add[10] ? 10'd1023 : add[9:0]

ex_code03a는 add[10] bit 가 1인지 아닌지를 비교하고, ex_code03b는 (in1+in2) 값이 1023과 큰지를 비교(11bits 비교기)합니다.

0

안녕하세요, 인프런 AI 인턴입니다. mjs1004님.

질문 주신 내용은 Verilog에서 동일한 연산을 수행하는 두 가지 방법을 비교하는 것에 대한 것입니다. ex_code03a와 ex_code03b 두 모듈은 각각 입력 in1과 in2를 덧셈하여 값이 1023 초과하면 결과를 1023으로 설정하고, 그렇지 않으면 계산된 합을 결과로 출력하는 기능을 합니다.

ex_code03a와 ex_code03b의 차이점:

ex_code03a:- 이 모듈은 덧셈 결과를 처리하기 위해 wire를 사용하며, 항상 블록 내에서는 결과 값을 최종 출력으로 저장하기 위해 register를 사용합니다.

- 이를 통해 연산을 분리할 수 있어 하드웨어 자원의 효율성을 극대화할 수 있으며, 결과 값을 연산 처리 내에서 유지할 수 있어 전체 연산 체인이 조직화 됩니다.

- 이 모듈은 덧셈 결과를 처리하기 위해 wire를 사용하며, 항상 블록 내에서는 결과 값을 최종 출력으로 저장하기 위해 register를 사용합니다.

ex_code03b:- 이 모듈은 wire 없이 항상 블록 내에서 직접 연산을 수행하고 결과를 저장하게 되어 있습니다.

- 모든 연산이 하나의 always 블록에서 일어남으로써, 연산 경로에 추가적인 지연시간을 유발할 수 있습니다.

- 이 모듈은 wire 없이 항상 블록 내에서 직접 연산을 수행하고 결과를 저장하게 되어 있습니다.

효율성의 이유:

ex_code03a의 효율성:

- 데이터 경로를 더 명확히 분리하여 병렬화하기 쉽고, 추가적인 레지스터를 사용해 안정적인 값 전달을 합니다. 이는 하드웨어 구현 시 파이프라이닝이나 레지스터의 빠른 주기 설정을 용이하게 만들어 효율적인 처리를 가능하게 합니다.

- 데이터 경로를 더 명확히 분리하여 병렬화하기 쉽고, 추가적인 레지스터를 사용해 안정적인 값 전달을 합니다. 이는 하드웨어 구현 시 파이프라이닝이나 레지스터의 빠른 주기 설정을 용이하게 만들어 효율적인 처리를 가능하게 합니다.

관련 공부 자료:

강의 자료의 37페이지를 통해 텍스트와 이미지 모두 검토해 보시면 각각의 코드가 하드웨어로 변환될 때 어떤 차이를 가지는지 더 명확히 이해하실 수 있습니다.

유사 질문 및 답변 링크:

- Verilog Code Optimization Techniques - 비슷한 코드 최적화 테크닉을 다루는 질문입니다.

위 질문은 Verilog에서의 최적화 방법 및 코드 관련 최적화 이유에 대한 이해를 돕습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

39

2

강의 만료일 연장 신청

0

42

2

기초예제 파일 불러오기 문의

0

30

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

33

2

혹시 별도의 자료가 있나요?

0

38

2

Zynq z7 FPGA single-ended 관련

0

42

1

Differential Amp의 4가지 종류

0

45

1

[HDL 22장] F/F CE 관련 질문

1

47

2

UART0, 1 중 선택

1

58

2

fpga 개발보드

0

31

2

vivado 2022.1 version memory IP 구조

0

41

1

datamoverbram모듈질문

1

66

2

latency 개념 구현

1

86

3

13강에 언급된 강의 내용 질문

1

62

2

비바도 all os버전

1

71

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

71

2

10 bits * 10bits 연산 구현 질문

0

245

1

강의문의

0

289

1

오타 및 내용 수정이 필요합니다.

0

316

1

alwayw구문의 작동 순서에 관해 문의드립니다.

0

281

2

parts 선택 관련 문의드립니다 !

0

330

1

FPGA MCU Porting

0

550

1

reg 선언 후

0

404

2

행렬과 관련하여 문의드립니다.

1

376

1