IP 생성 시 어드레스 오류

안녕하세요, 맛비님!

zybo z7 10보드

vivado, vitis 2022.2 버전 사용중입니다.

해당 수강생님과 같은 문제가 발생했지만 일단 강의를 끝까지 따라가보았습니다.

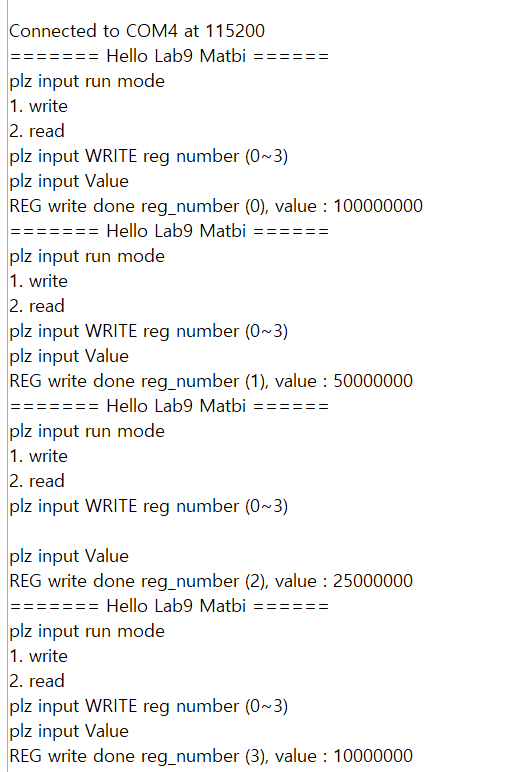

write 과정

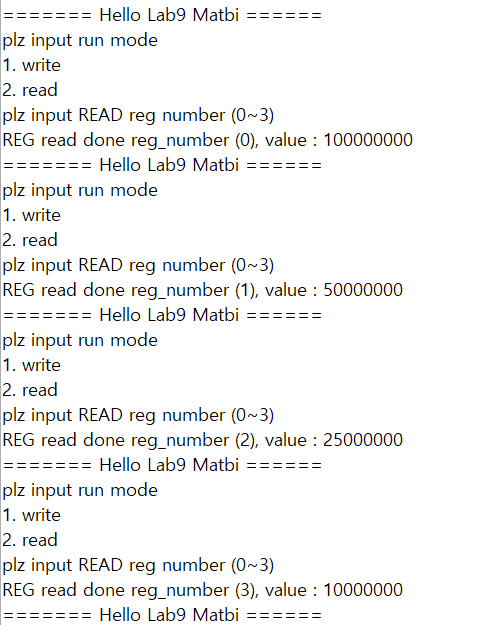

read 과정

이렇게 read & write 과정 모두 잘 진행되고 보드 led 점등도 설정한 속도대로 잘 동작합니다.

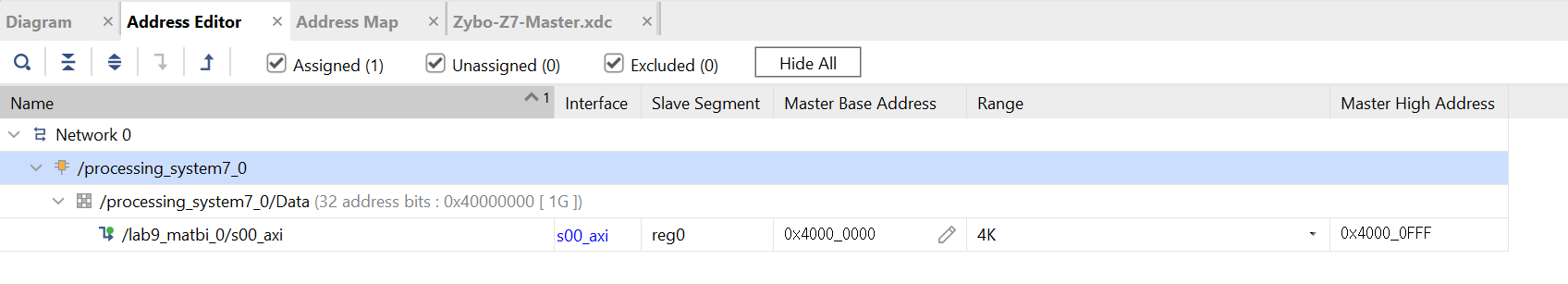

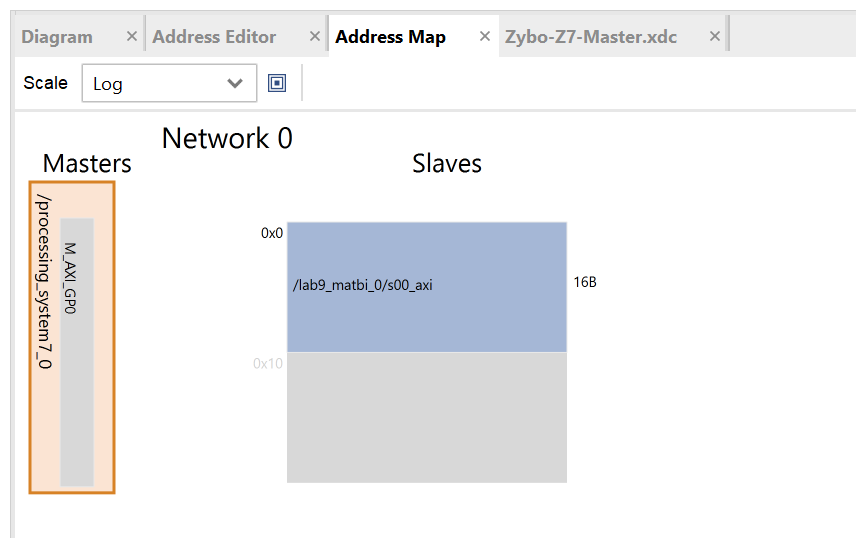

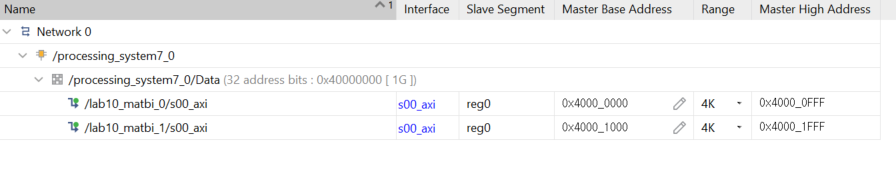

다음과 같이

다른 주소값, 범위가 할당되는 것은 문제가 되지 않을까요??

lab10 에서도 같은 문제 발생합니다.

터미널에서 수행은 문제없이 잘됩니다.

답변 2

0

안녕하세요 🙂

질문을 정확하게 이해한건지는 모르겠는데요.

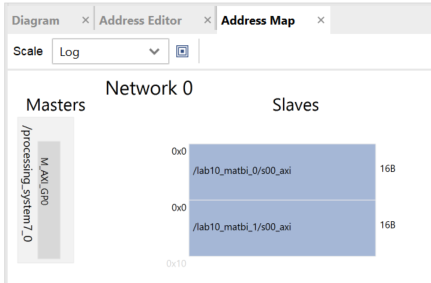

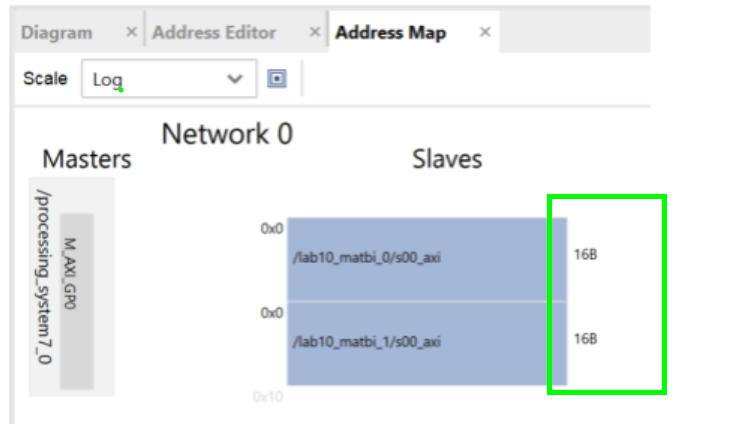

size 부분을 편집할 수 있으면 좋겠는데, 현재 16B 로 size 가 잡혀있는 것 같아요.

16 Byte 면 4 개의 register 를 사용할 수 있는데요.

다행히? 강의에서 4개만 사용중인지라, 동작에는 문제가 없어보여요.

PS 영역에서 접근할 수 있는 baseaddr 와 size 가 정확하다면 큰? 문제는 없을 것 같습니다.

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다. info님!

Vivado에서는 종종 자동으로 설정된 IP의 주소/범위가 원하는 값과 다르게 할당될 수 있습니다. 이는 툴의 기본 설정값이 다르게 설정될 수 있기 때문입니다. 하지만, 문제가 되지 않는다면 시스템 설계 상으로는 특별한 문제가 없을 수 있습니다.

기본적으로, IP가 의도한 대로 동작하고 read 및 write 과정에서 원하는 값이 제대로 전달되어 시스템이 정상적으로 동작한다면 큰 문제는 아닙니다. 그러나, 특정한 주소나 범위가 필요한 상황이라면 수동으로 주소 설정을 수정할 수 있습니다. 기본적으로 Vivado에서 제공하는 인터페이스를 통해 특정 Register의 Base 주소를 수동으로 설정할 수 있으니, 필요하실 경우 이에 맞추어 설정을 진행하시기 바랍니다.

기존에 유사한 질문들에 대한 참고답변들을 드리겠습니다.

“Addresss와 Memory write error에 관련되어 질문이 있습니다”:

- 여기에서는 xparameters 헤더 파일에서 baseaddress 수정과 high address 수정을 제안하고 있습니다.

- 여기에서는 xparameters 헤더 파일에서 baseaddress 수정과 high address 수정을 제안하고 있습니다.

“HW IP 생성 시 IP address의 range 관련 질문”:

- AXI4의 설정과 Vivado에서 제공하는 GUI 설정에 대해 안내합니다.

- AXI4의 설정과 Vivado에서 제공하는 GUI 설정에 대해 안내합니다.

혹시나 툴의 설정이 잘못되어 있어 수동으로 설정해야 한다면, 수업의 해당 부분을 참고하시거나 Instructor가 제공한 파일을 다시 확인해 보시면 많은 도움이 될 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

UART0, 1 중 선택

1

58

2

datamoverbram모듈질문

1

66

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

101

2

vitis 설치 관련 질문 있습니다!

1

87

2

FPGA 공식문서 읽는법

1

99

2

보드 추가의 클릭창이 없습니다.

1

72

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

83

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

108

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

295

3

[9장 led 점등 시간 제어 불가]

1

83

2

Platform Invalid 오류

1

152

3

WSL 설치 관련 문의드립니다!!

1

98

2

Vivado 툴, 파일 질문드립니다!

1

157

2

9장 LED 점등 안됨

1

113

3

Edit in IP Packager 이후에

1

88

1

Fpga 로직

1

92

2

pmu-fw is not running

1

128

2

Create Project에 대해서 궁금해요

1

91

2

장치관리자 USB 포트

1

102

2

FPGA 7장 AXI_LITE I/F질문

1

91

1

bram mover에서 합성할때

1

80

2

타이밍 위반 질문

1

81

2

rvalid 초기화

1

68

2