21강 질문 - Fully Connected Layer C 계산 이해에 관하여

248

작성한 질문수 1

안녕하세요, 맛비님

먼저 좋은 강의 감사합니다.

수강 후 개인 복습 중 이상해 보이는 점을 질문 드립니다.

Fully Connected Layer 개념 설명에서 "weight 개수 = input node 수 x ouput node 수" 라고 설명하여 주셨는데

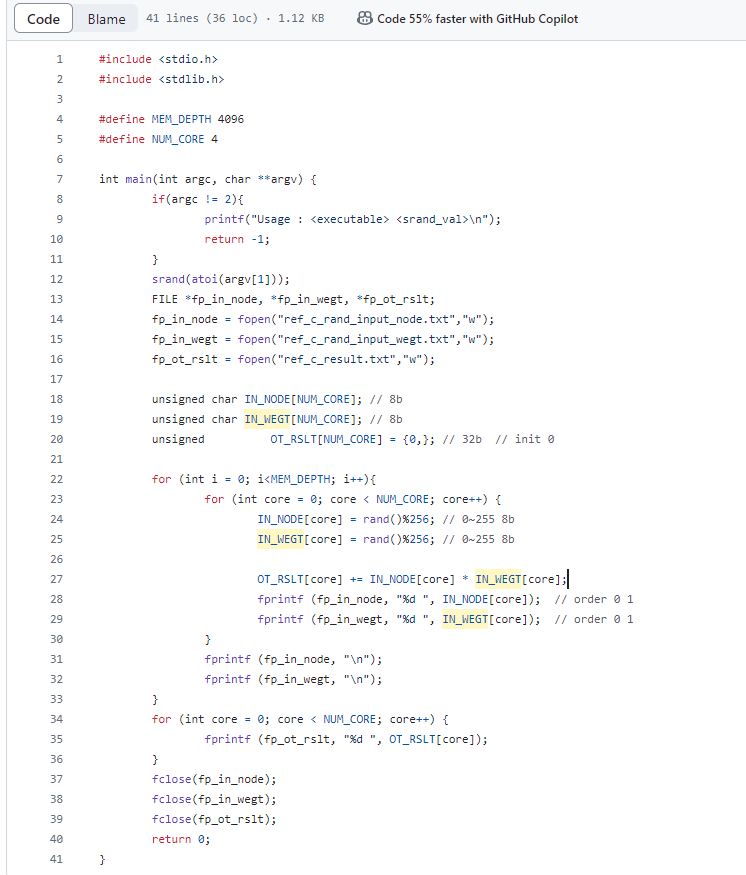

21 강 C 코드를 보면 input node의 수를 4096 개, output node의 수는 4개로

필요한 weight 수는 총 4096*4 개 필요함을 알 수 있었습니다.

그러나 C코드의 반복문 계산을 보면 input node 수도 weght 와 같이 4096*9 만큼 발생되어 Fully Connected Layer 연산에 착오가 생기는 듯 싶습니다.

혹시 제가 이해하고 있는 내용이 맞는지 설명해주실 수 있을까요???

답변 2

0

안녕하세요 🙂

제가 질문을 정확하게 이해 못한 것 같은데요.

다음 코드에서, input node 가 "9" 라는 숫자가 발생하는 부분이 어디 인지 알려주실 수 있을까요??

0

아.. 이해했습니다.

말씀해주신대로, input node 전부를 rand 로 생성하기 때문에, 4096*4 개가 생성이 되네요. 4096 개의 input node 만 rand 로 생성하고, weight 를 4096*4 개만큼 rand 로 생성해서, output 을 4개만 나오게 accum 하는 것이 맞습니다.

C 부분만 수정이 되면 될 것 같습니다. 수정해보면, 다음과 같습니다.

해당 부분은 강의 노트 밑에 남겨두겠습니다.

unsigned char IN_NODE[MEM_DEPTH]; // 8b

for (int i = 0; i<MEM_DEPTH; i++){ // input node 4096 개 생성

IN_NODE[i] = rand()%256; // 0~255 8b

}

for (int i = 0; i<MEM_DEPTH; i++){

for (int core = 0; core < NUM_CORE; core++) {

IN_WEGT[core] = rand()%256; // 0~255 8b

OT_RSLT[core] += IN_NODE[i] * IN_WEGT[core];

fprintf (fp_in_node, "%d ", IN_NODE[i]); // order 0 1

fprintf (fp_in_wegt, "%d ", IN_WEGT[core]); // order 0 1

}

fprintf (fp_in_node, "\n");

fprintf (fp_in_wegt, "\n");

}

찾아주셔서 감사합니다!!

명확하게 그 당시에 썼어야 했는데, 애매했네요;; (이미 찾아주신 분이 계셨었는데 ㅠ)

input node 개수에 따른 연산 오류 리포팅: https://inf.run/2xrK

0

안녕하세요, 인프런 AI 인턴입니다.

질문하신 내용은 프로그래밍 또는 하드웨어 설계의 구체적인 코드 분석이나 이해와 관련된 것으로 보입니다. 제공된 정보 중에는 프로그래밍, 하드웨어 설계 관련 직접적인 내용이 없어, 해당 질문에 대해 직접적인 답변을 드리기 어려움을 알려드립니다.

이 내용과 관련해서는 강의를 제공한 플랫폼이나 강사에게 직접 문의하시거나, 해당 기술에 대한 특정 포럼이나 커뮤니티에 질문하시는 것이 좋을 것 같습니다.

추가적인 도움이 필요하시면 질문 내용을 구체화하여 다시 문의 부탁드립니다.

UART0, 1 중 선택

1

49

2

datamoverbram모듈질문

1

62

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

84

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

70

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

288

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

145

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

150

2

9장 LED 점등 안됨

1

109

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

89

2

pmu-fw is not running

1

126

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2