FPGA 16장의 AXI_awaddr에 대해 질문 있습니다!

403

작성한 질문수 2

항상 좋은 강의 감사드립니다!

다름이 아니라 16장에서 AXI_awaddr의 값이 변화하는 과정에 대해서 질문이 있어서 문의드립니다!

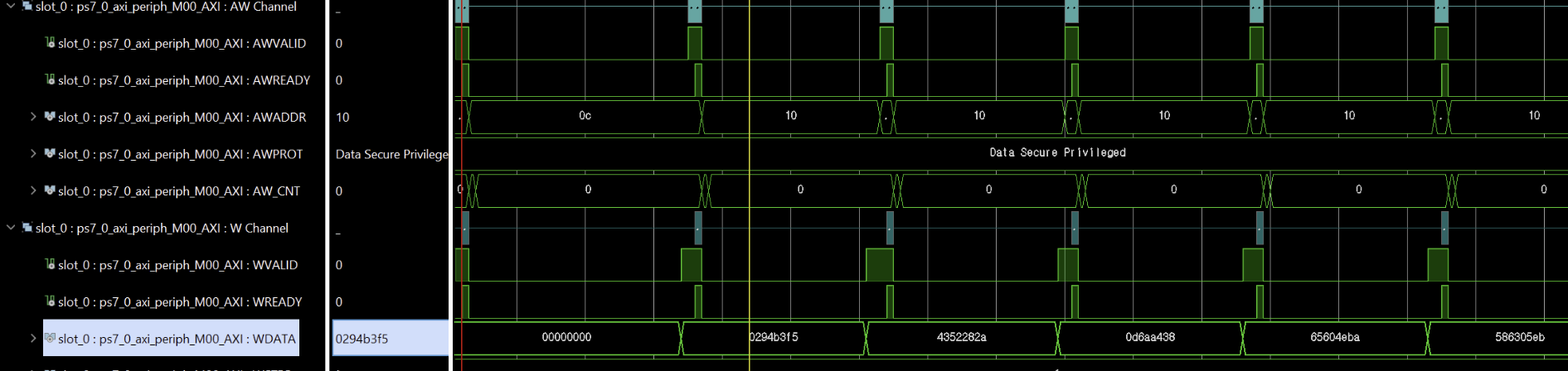

AXI의 address 값이 0x08일 때는 BRAM의 주소 값을 초기화하고, 0x0c일 때는 BRAM의 특정 데이터를 넣어준 뒤 BRAM의 주소 값을 다음으로 넘어가게 한다는 것은 이해하였고, 그 부분이 코드에서 동작하는 것 역시 볼 수 있었습니다. 위 사진의 AWADDR에서도 10과 10 사이에 작게 보이지 않는 부분이 0x0c입니다.

AXI의 address 값이 0x08일 때는 BRAM의 주소 값을 초기화하고, 0x0c일 때는 BRAM의 특정 데이터를 넣어준 뒤 BRAM의 주소 값을 다음으로 넘어가게 한다는 것은 이해하였고, 그 부분이 코드에서 동작하는 것 역시 볼 수 있었습니다. 위 사진의 AWADDR에서도 10과 10 사이에 작게 보이지 않는 부분이 0x0c입니다.

하지만 사진에서 보다시피 데이터가 write되는 구간과 구간 사이에서 AWADDR이 0x10으로 변했다가 다시 0x0c로 변하는 현상이 발생하였고, 이렇게 동작하는 부분이 어디인지 주어진 코드를 분석했지만 그 부분을 찾지 못해서 질문드립니다. 어느 코드의 어느 부분에서 AWADDR이 0x0c->0x10->0x0c로 동작하는지 알려주시면 감사하겠습니다!

답변 1

0

안녕하세요 :)

Ready / Valid Handshake 가 발생할때는 0x0c 만 되는 것으로 보아, 정상동작하고 있고요.

어느 코드의 어느 부분에서 AWADDR이 0x0c->0x10->0x0c로 동작하는지 알려주시면 감사하겠습니다!

결론부터 말씀드리면, 예제 코드에서 0x10 을 만들어내는 것이 아니다. 입니다. 자세히 살펴보죠.

==========================================================

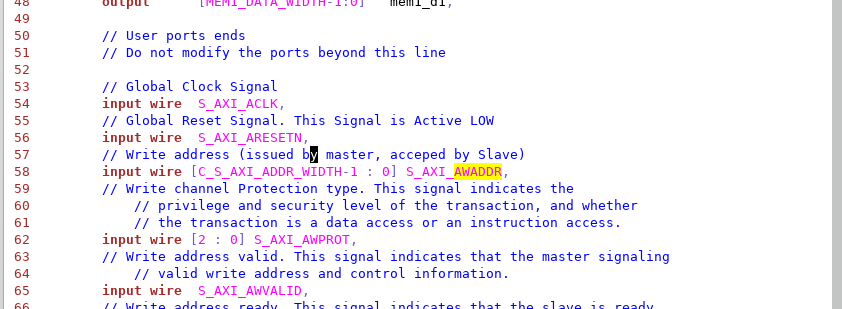

HW 를 보면

현재 코드를 보시면, HW 는 AWADDR 은 input 입니다.

즉, 10 으로 변하는 현상은 HW 가 만드는 현상이 아닌거죠.

SW 를 보면

SW 코드내부에서는 for loop 으로 0x0c 로만 Write 하도록 코딩이 되어있죠.

그럼 누가..? 그렇게 만드는 걸까요?

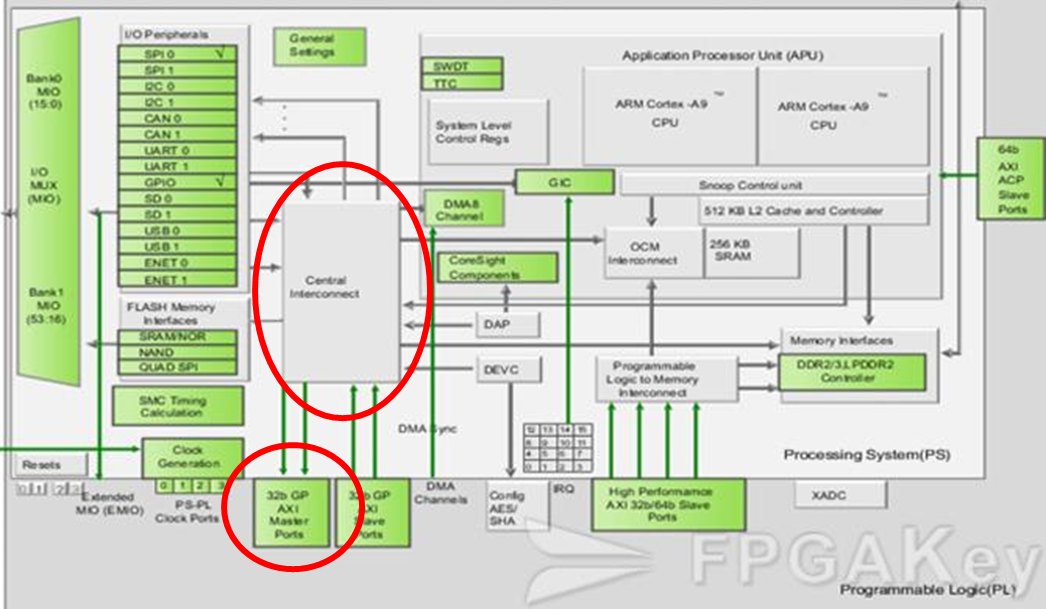

PS -> PL (16장 모듈) 로 Data 가 전송되고 있고요.

PS 내부에는 AXI4-Lite Master 동작을 위한 HW 로직이 있습니다.

Central Interconnect 에는 많은 AXI Port 들이 연결이 되어 있고요.

이는 다양한 Address 를 접근합니다. AWADDR 이 여러개 물려있다는 뜻과 같죠.

그래서 Interconnect 내부에 남아있던 잔여 AWADDR data 가, AXI4-Lite Port 의 AWADDR 에 보여진게 아닌가 추측합니다. (PS 내부의 다른 HW 모듈이 0x10 을 접근한것이 아닌가 하는 추측? 누군지는 저도 잘 모르겠네요.)

0x10 으로 변경되어도, Handshake 가 발생하는 시점의 Data 들을 보기때문에, 동작에는 아무 문제는 없습니다.

결론

예제코드에서 변경하는 것이 아닌, PS 내의 HW 모듈이 0x10 을 만들어 내었다.

즐공하세요 :)

UART0, 1 중 선택

1

50

2

datamoverbram모듈질문

1

63

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

84

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

70

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

289

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

145

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

150

2

9장 LED 점등 안됨

1

109

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

89

2

pmu-fw is not running

1

126

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2