PCIe 통신

1064

작성한 질문수 1

안녕하세요.

강의 잘 듣고 있습니다.

강의에서는 zybo보드 위의 PS를 사용하고 있는데,

제가 사용하고 있는 보드에는 PS가 없습니다.

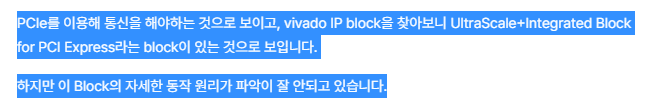

PCIe를 이용해 통신을 해야하는 것으로 보이고, vivado IP block을 찾아보니 UltraScale+Integrated Block for PCI Express라는 block이 있는 것으로 보입니다.

하지만 이 Block의 자세한 동작 원리가 파악이 잘 안되고 있습니다.

혹시 PC와 board간의 PCIe 통신을 어떻게 하는지에 대한 documentation이 있다면 추천 가능하실까요?

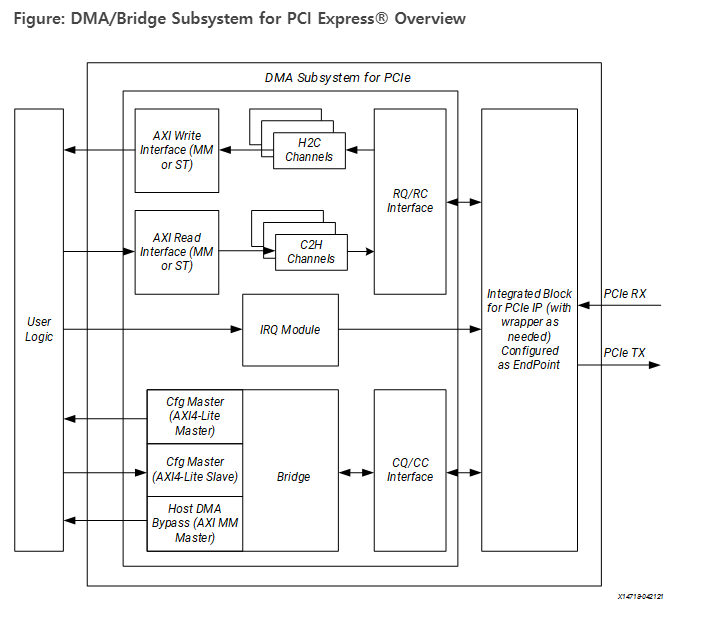

또한 강의 실습들에서 clock을 PS에서 생성하도록 하였는데, PC에서의 clock을 받아오는 경우에 대한 설명이 있다면 소개 부탁드리겠습니다.

Xilinx documentation에 모든 설명이 나와있을 거라고 생각하지만, 제가 이 분야가 처음이고, documentation들이 워낙 방대한지라 도움을 요청합니다.

감사합니다.

답변 1

1

안녕하세요 :)

강의 내용외의 질문은 받고있지 않다라는 점 양지 부탁드립니다.

참고용으로 봐주세요.

Q1

PCIe 의 XDMA 라는 HW IP 가 존재합니다. (https://docs.xilinx.com/r/en-US/pg195-pcie-dma/Overview?tocId=O_EMX26J5IsdubL4i3XJ_w)

PCIe 의 XDMA 라는 HW IP 가 존재합니다. (https://docs.xilinx.com/r/en-US/pg195-pcie-dma/Overview?tocId=O_EMX26J5IsdubL4i3XJ_w)

이를 통해서 통신합니다.

PCIe -> XDMA -> AXI4

Q2

xdma ip 에 clock port 가 별도로 존재하네요. 이거를 사용하시면 됩니다.

xdma ip 에 clock port 가 별도로 존재하네요. 이거를 사용하시면 됩니다.

즐공하세요 :)

UART0, 1 중 선택

1

50

2

datamoverbram모듈질문

1

63

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

84

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

70

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

289

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

145

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

150

2

9장 LED 점등 안됨

1

109

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

89

2

pmu-fw is not running

1

126

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2