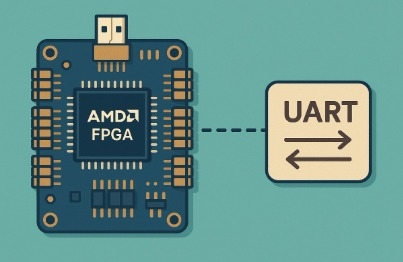

FPGAにUARTを実装する

UARTは最も基本的で広く活用されているシリアル通信方式であり、FPGA設計に初めて触れる初心者にとって非常に適した学習テーマです。本講義では、UARTの通信原理とフレーム構造を詳細に理解し、これを基にRTL(Register Transfer Level)設計を通じて送受信ロジックを直接実装する過程を進めます。FPGA上でUARTを実装することで、デジタル回路設計能力を体系的に養い、シミュレーションおよび検証を通じて実際のハードウェアレベルでの動作を確認する経験を積むことができます。また、Soft ProcessorであるMicroBlazeとXilinx UART IPを活用した方式も共に学習し、プロセッサベースのシステム設計フローおよびインターフェース構成を幅広く理解するようになります。これにより、論理設計とプロセッサ設計を網羅する包括的な開発能力を身につけることができます。

- 解決

Zybo 환경에서 PL RTL UART 보드 검증 방법

안녕하세요, 강의 수강 중 문의드립니다. * 저는 아직 이해가 부족한 부분이 많아 질문 내용을 AI의 도움을 받아 정리하였습니다.<p

fpgasystem-veriloguartvivadomini9136

・

15日前

0

31

2

- 未解決

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다.

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다. 아님 맨처음에 설정에서 보드 설정이 있는데 그걸로도 가능한지 궁금합니다.

fpgasystem-veriloguartvivadolemmon78198028

・

2ヶ月前

0

63

1

- 解決

5장 강의 노트 확인 부탁드립니다.

5. UART TX/RX 모듈 RTL 설계 및 시뮬레이션강좌의 강의 자료를 다운 받으면 ep06_Intergration 자료 입니다.확인 부탁드립니다.</

fpgasystem-veriloguartvivadoinair3292

・

7ヶ月前

0

68

2

- 解決

RTL

RTL이 Veliog인거같은데 vhdl 버전은 없나요 ?

fpgasystem-veriloguartvivadoflak397306

・

8ヶ月前

0

98

1

- 解決

멀티바이트프레임 로직 예시

FIFO를 이용하여 멀티바이트프레임 로직 구문을 작성 및 처리하는 참조 할 만한 로직 예시 가 있을까요

fpgasystem-veriloguartvivadojookd787339

・

8ヶ月前

0

90

2