Inflearn Community Q&A

top module / 내부 모듈, register 하위 2비트 사용하지 않는다.

Resolved

Written on

·

675

1

Quiz

AXI4-Lite 인터페이스는 하드웨어 IP 제어 시 주로 어떤 목적으로 사용될까요?

대용량 데이터의 고속 스트리밍 전송

하드웨어 IP의 내부 레지스터 설정 및 상태 확인

메모리 간의 복잡한 데이터 전송 프로토콜 구현

여러 칩 간의 동기화되지 않은 통신

Answer 2

1

top은 testbench랑 다른거였군요.. 감사합니다!

바이트를 4bit라고 적다니.. 반성하자.. 8bit!!

내부로 접근할 때는 같은 4byte 이니 하위 2bit가 필요없다. 여기는 이해가 되었습니다.

최종적으로 AXI interface 의 address 는 byte 단위이므로 하위 2bit을 추가하였다.. 이 부분이 이해가 가지 않습니다...ㅠ

2'h0 -> h가 의미하는게 hexa 맞나요?? 2'b00으로 표현해도 되는 건가요?

아 내부로 들어가는 것도 잘 못 이해했군요!

내부로 들어갈때 4를 표현하기 위해서 LSB로 표현한 코드를 이용해 하위 2비트를 따로 빼놓고 사용.

다시 나갈때는 뺏던 2bit을 추가해서 원래상태로 추가해서 나간다.

맞을까요?? (제발 맞기를!!)

문법은 혹시 저렇게도 변경가능한가 궁금해서 여쭤봤습니다^^

늦은시간 까지 공부를! 훌륭하십니다.

"내부로 들어갈때 4를 표현하기 위해서 LSB로 표현한 코드를 이용해 하위 2비트를 따로 빼놓고 사용. 다시 나갈때는 뺏던 2bit을 추가해서 원래상태로 추가해서 나간다."

굿! 정확하게 맞습니다. (내부에서 2 bit 을 빼면 조금이라도 사용하는 로직을 줄일 수 있겠죠?)

하지만, 이정도 까지 안하는 경우가.. 많으실꺼에요. 동작하는 것을 만드는게 더 중요해서.. ㅎ

"문법은 혹시 저렇게도 변경가능한가 궁금해서 여쭤봤습니다^^"

네네 이렇게 하셔도 돼요.

2'b00, 2'o0, 2'd0, 2'h'0

즐공하셔요 :)

1

안녕하세요. :)

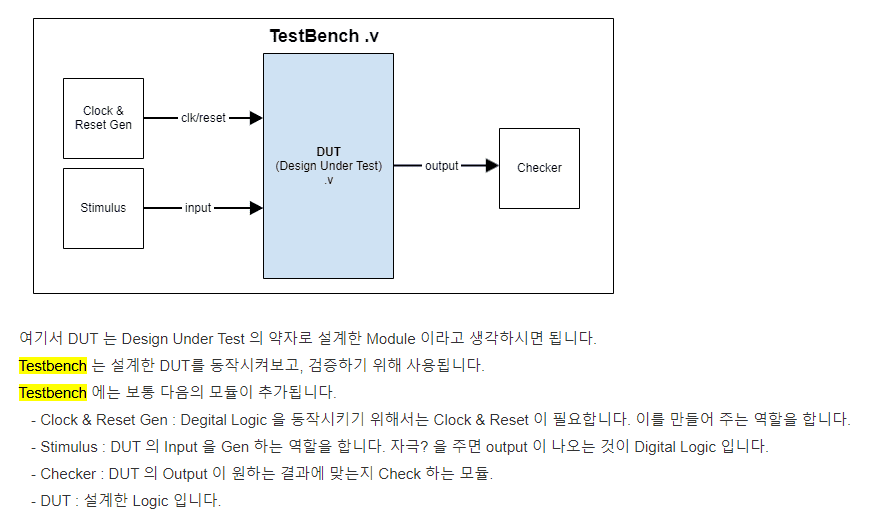

testbench 는 testbench 이구요.

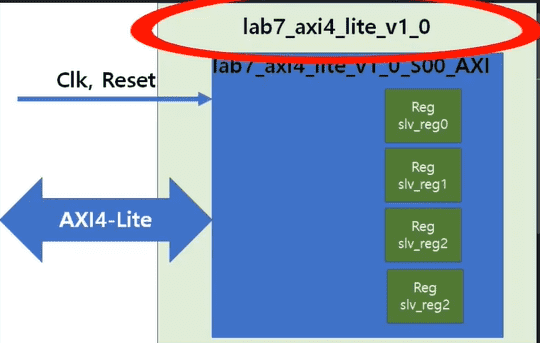

DUT의 Top 은 lab7_axi4_lite_v1_0 입니다.

이 개념은 다음 저의글? 을 참고해보세요.

먼저 Address 단위는 Byte (8bit) 입니다. (4bit 아니에요)

AXI4-Lite 의 Databit 는 32bit 즉, 4 byte 입니다.

이는 Address 에서 하위 2bit 이 없어도 접근 가능하다는 뜻이죠.

(하위 2bit 로 4 를 표현 할 수 있으니까요.)

최소 Address 단위가 4byte 이기 때문에 하위 2bit 가 없어도 접근 가능한 상태입니다.

하지만 최종적으로 AXI 의 Address 로 나갈때는 Byte 단위이기 때문에

2'h0 을 하위 bit 에 붙여서 접근해야죠.

결론

4byte 의 주소접근이 가능한 상태 (Data 가 4byte 32bit 이기 때문에) 에서 내부에서는 하위 2bit 이 없어도 접근 가능하다.

하지만 최종적으로 AXI Interface 의 Address 는 Byte 단위이므로 (4byte 아님) 하위 2bit 을 추가하였다.

즐공하세요 :)

헛.. 제가 글을 쓰는 중이라 바로 답변드립니다. ㅎ

풀어서 적어볼께요.

내부에서는 하위 2bit 를 제외하고 사용중이었죠.

하지만 외부로 나가는, AXI Interface 의 Address 는 Byte 단위입니다. (왜 Byte 냐면, AXI Protocol 이 그래요!)

그래서 기존의 하위 2 bit 을 뺏던 부분을!!, 하위 2bit 을 다시 추가해서 byte 단위로 맞춰주었습니다.

2'h0 -> h가 의미하는게 hexa 맞나요?? 2'b00으로 표현해도 되는 건가요?

(이거는 Verilog HDL 의 문법인지라.. 꼭!! 책을 공부해주세요)

hexa 맞구요. 2'b00 표현하셔도 돼요 :)

그럼 즐공하세요 :)