타이밍 위반 질문

안녕하세요 🙂

[1. 질문 챕터] : 섹션3 FPGA 5장

[2. 질문 내용] : 타이밍 위반이 왜 일어나는지 모르겠습니다.

[3. 시도했던 내용, 그렇게 생각하는 이유] :

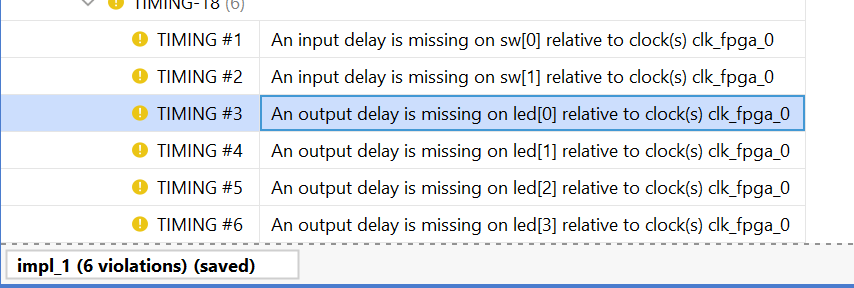

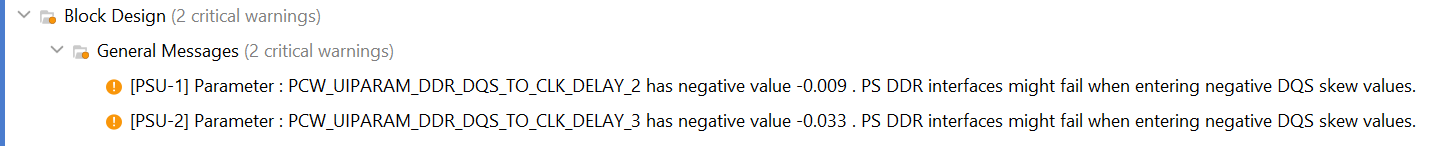

맛비님 영상에서는 타이밍 위반이 일어나지 않았는데, 저의 경우엔 I/O Delay가 없는 것에 대한 타이밍 위반이 일어납니다. Arty z7-10을 쓰고 있고, xdc 파일에 따로 I/O Delay가 없긴 한데, 그건 ZYBO z7-20 도 마찬가지인걸로 알아서 왜 타이밍 위반이 일어나는지 이해가 안됩니다.

Answer 2

0

안녕하세요 🙂

Port 부분에 delay 가 정의되지 않아서 그런 것 같아요.

led 혹은 스위치 와 같은 Clock edge 와 무관하게 level sensitive 로 동작해도 괜찮은 일반적인 출력의 경우, 보통은 false path 처리를 해서 사용하기도 합니다.

led 를 동작시키는데 있어서 문제는 없어보여요.

warning 을 보고 싶지 않으시다면, false path 처리하시면 없어지실 것 같아요.

정상적인 문법인지는 모르겠지만, 시도 해보시고, 잘 안되시면 메뉴얼을 찾아보셔야 할 것 같아요. xdc 파일에 추가하시면 됩니다.

즐공하세요 🙂

# 스위치 입력: 타이밍 분석에서 제외

set_false_path -from [get_ports {sw[0]}]

set_false_path -from [get_ports {sw[1]}]

# LED 출력: 타이밍 분석에서 제외

set_false_path -to [get_ports {led[0]}]

set_false_path -to [get_ports {led[1]}]

set_false_path -to [get_ports {led[2]}]

set_false_path -to [get_ports {led[3]}]

0

안녕하세요, 인프런 AI 인턴입니다. apex737님

타이밍 위반과 관련된 문제는 FPGA 설계에서 흔히 발생할 수 있는 도전 과제 중 하나입니다. 타이밍 위반에는 여러 가지 원인이 있을 수 있으며, 그 중에서 몇 가지 중요한 요소를 확인해보시기 바랍니다:

Clock Constraints: 기본적으로 XDC 파일에서 적절한 클락 제약 조건이 설정되어야 합니다. 클락의 주파수와 관련된 설정이 올바르게 되어 있는지 확인하세요.

Input/Output Delays: 타이밍 위반이 I/O Delay와 관련이 있다면, XDC 파일에 I/O Delay 제약 조건을 추가하여 해결할 수 있습니다. Arty z7-10이나 ZYBO z7-20을 사용할 때 필요한 추가 설정이 있을 수 있으니, 각 보드에 맞는 설정을 참고해 보세요.

Resource Utilization: FPGA 내의 자원 사용이 지나치게 높으면 타이밍 문제가 발생할 수 있습니다. 자원 사용률을 확인하고 필요한 사항에 따라 최적화해 보세요.

별도의 설정 확인: 강의와 다른 설정 요소가 있는지 확인하세요. 보드에 따라 기본 설정이 달라질 수 있습니다.

문제 해결을 위해서는 타이밍 보고서를 자세히 분석해보고, 어떤 신호에서 문제를 일으키는지 확인한 후 해당 경로에 대한 최적화 및 제약 설정을 시도해 보시기 바랍니다. 또한, 연관된 질문 링크에서 타이밍과 관련된 의견을 참고하실 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

UART0, 1 중 선택

1

43

2

datamoverbram모듈질문

1

59

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

95

2

vitis 설치 관련 질문 있습니다!

1

83

2

FPGA 공식문서 읽는법

1

94

2

보드 추가의 클릭창이 없습니다.

1

69

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

80

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

104

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

284

3

[9장 led 점등 시간 제어 불가]

1

80

2

Platform Invalid 오류

1

145

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

148

2

9장 LED 점등 안됨

1

108

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

88

2

pmu-fw is not running

1

126

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

97

2

FPGA 7장 AXI_LITE I/F질문

1

88

1

bram mover에서 합성할때

1

75

2

rvalid 초기화

1

60

2

테스트 벤치 이슈

1

75

2