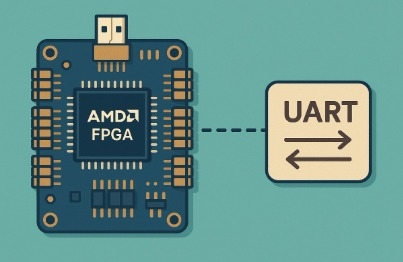

FPGA에 UART 구현하기

UART는 가장 기본적이며 널리 활용되는 시리얼 통신 방식으로, FPGA 설계를 처음 접하는 입문자에게 매우 적합한 학습 주제입니다. 본 강의에서는 UART의 통신 원리와 프레임 구조를 상세히 이해하고, 이를 기반으로 RTL(Register Transfer Level) 설계를 통해 송수신 로직을 직접 구현해보는 과정을 진행합니다. FPGA 상에서 UART를 구현함으로써 디지털 회로 설계 능력을 체계적으로 키우고, 시뮬레이션 및 검증을 통해 실제 하드웨어 수준에서 동작을 확인하는 경험을 쌓을 수 있습니다. 또한 Soft Processor인 MicroBlaze와 Xilinx UART IP를 활용한 방식도 함께 학습하여, 프로세서 기반의 시스템 설계 흐름 및 인터페이스 구성을 폭넓게 이해하게 됩니다. 이를 통해 논리 설계와 프로세서 설계를 아우르는 포괄적인 개발 역량을 갖출 수 있습니다.

- 해결

Zybo 환경에서 PL RTL UART 보드 검증 방법

안녕하세요, 강의 수강 중 문의드립니다. * 저는 아직 이해가 부족한 부분이 많아 질문 내용을 AI의 도움을 받아 정리하였습니다.<p

fpgasystem-veriloguartvivado아크3

・

14일 전

0

31

2

- 미해결

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다.

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다. 아님 맨처음에 설정에서 보드 설정이 있는데 그걸로도 가능한지 궁금합니다.

fpgasystem-veriloguartvivado먹구름

・

2달 전

0

62

1

- 해결

5장 강의 노트 확인 부탁드립니다.

5. UART TX/RX 모듈 RTL 설계 및 시뮬레이션강좌의 강의 자료를 다운 받으면 ep06_Intergration 자료 입니다.확인 부탁드립니다.</

fpgasystem-veriloguartvivadoIN_AIR_HW

・

7달 전

0

68

2

- 해결

RTL

RTL이 Veliog인거같은데 vhdl 버전은 없나요 ?

fpgasystem-veriloguartvivadoJiYoung

・

8달 전

0

98

1

- 해결

멀티바이트프레임 로직 예시

FIFO를 이용하여 멀티바이트프레임 로직 구문을 작성 및 처리하는 참조 할 만한 로직 예시 가 있을까요

fpgasystem-veriloguartvivado미키루크

・

8달 전

0

90

2