인프런 커뮤니티 질문&답변

안녕하세요 선생님!

작성

·

385

0

인텔과 AMD의 경우 CPU의 순차적 일관성을 원래부터 보장한다고 말씀해주셨는데 이것이 atomic 클래스가 아닌 자료형에 대한 연산 또한 마찬가지인지 궁금해요.

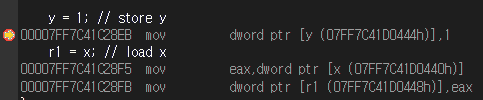

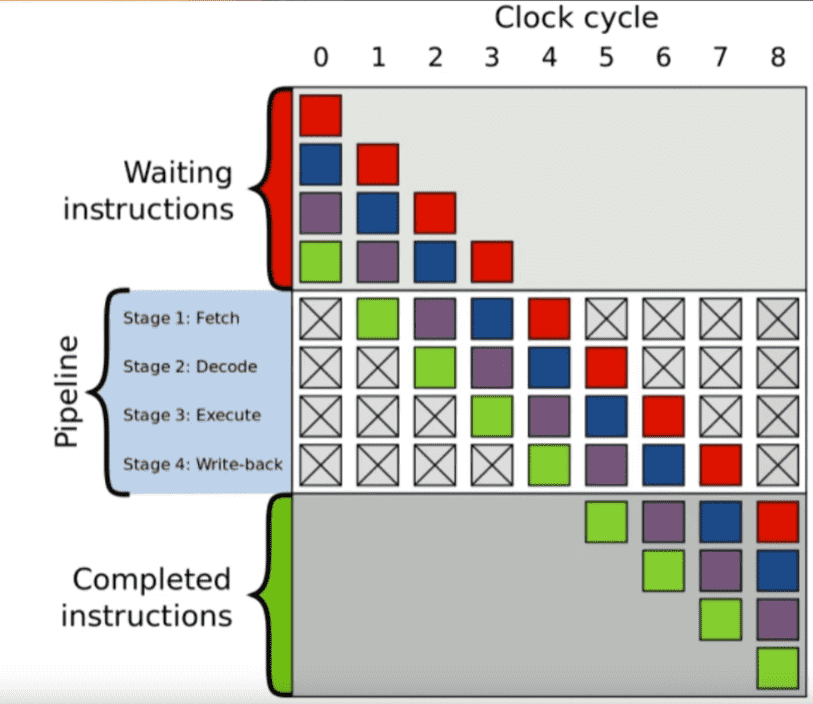

또한 순차적 일관성이라는 의미가 저번에 설명해주신 CPU 파이프라인 상에서 저 네모들의 위치가 변경되지 않는다는 것을 말씀하신 것인지 알고 싶어요.

그게 맞다면 저번에 예제로 주신 아래의 코드가 CPU 파이프라인 단에서는 어셈블리의 실행 순서가 변경되는 최적화가 일어나지 않는 것인지 알고 싶어요.

해당 어셈블리를 살펴보면 컴파일러 단에서도 최적화를 하지 않는데도 언젠가 빠져나오는 것 보면 이것은 단순히 RAM에 최신정보가 반영되지 않은 메모리 가시성의 문제인지 알고 싶어요!

#include "pch.h"

#include <iostream>

#include <thread>

#include <atomic>

#include <mutex>

#include <future>

#include <windows.h>

int32 x = 0;

int32 y = 0;

int32 r1 = 0;

int32 r2 = 0;

volatile bool ready;

void Thread1()

{

while (!ready);

y = 1; // store y

r1 = x; // load x

}

void Thread2()

{

while (!ready);

x = 1; // store y

r2 = y; // load y

}

int main()

{

int32 count = 0;

while (true)

{

ready = false;

count++;

x = y = r1 = r2 = 0;

thread t1(Thread1);

thread t2(Thread2);

ready = true;

t1.join();

t2.join();

if (r1 == 0 && r2 == 0)

break;

}

cout << count << " 번만에 빠져나옴" << endl;

}퀴즈

66%나 틀려요. 한번 도전해보세요!

멀티쓰레딩 환경에서 여러 쓰레드가 동시에 공유 데이터에 접근하여 값을 수정할 때 발생할 수 있는 예상치 못한 결과의 주요 원인은 무엇일까요?

데드락

쓰레드 지역 저장소(TLS) 충돌

경쟁 상태(Race Condition)

CPU 파이프라인 실패

답변 1

1

Rookiss

지식공유자

순차적 일관성은 CPU의 파이프라인이나 실행 순서에 대한 얘기가 아니고,

캐시랑 연관성이 있는 부분입니다.

CPU 코어마다 캐시가 따로 있으니,

표준에 의하면 모든 코어마다 동일한 값을 관찰하지 못할 수도 있는데

인텔 환경에서는 의외로(?) 수정된 값을 읽는 것을 확인할 수 있습니다.