SRAM Interface Behavior(Diagram) 질문

1) Interface bahavior에서 BWEn에 대한 역할이 궁금합니다

2)CSn=WEn=0 직후 해당 칩에 대해서 write가 진행될텐데, 여기서 addr 부분이 제가 이해한게 맞는 것인지 궁금합니다.

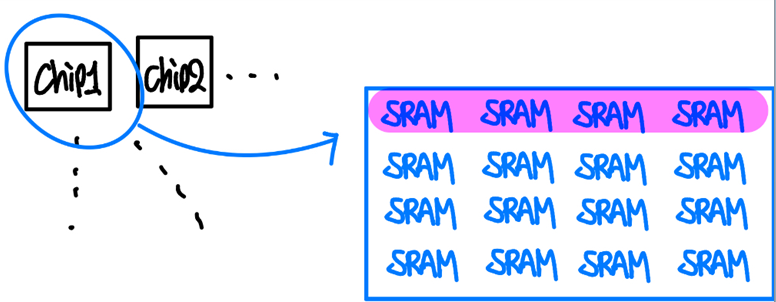

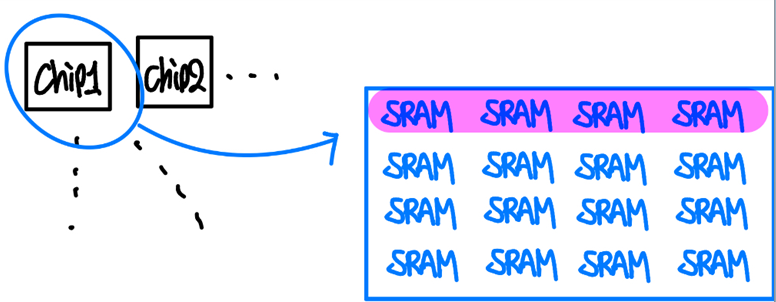

제가 이해한 바로는 여러 개의 SRAM 칩이 있을테고, 그러한 SRAM 칩에는 또다시 Width*Depth로 Cell 단위의 SRAM 쭉 나열 되어 있고, 그 중 한 행만을 선택하여 write를 진행하는 것인지 궁금합니다. 예컨대, 이 그림과 같이 수 많은 칩이 존재할 때, 특정 칩을 CSn=0으로 만들고, WEn=0으로 만들어 write 가능하게 만들고, 그리고 그 칩 내부로 들어가서 CELL Array 중 첫번째 행을 선택하고 싶다면 addr=0으로 만들어주는게 맞는건가요?

3) 또한 wdata에 대해 inner_mem은 왜 delay되어 나오고, rdata에 대해 inner_mem은 왜 곧바로 나오는지 궁금합니다. wdata를 din으로 보고, rdata를 dout, inner_mem를 Chip 내부 메모리로 보면, 결국 din에서 inner_mem로 들어가는 시간이나 dout에서 inner_mem으로 나가는 시간은 둘 다 delay가 있을 것으로 보이는데, 저의 해석이 잘못된건가요??

답변 3

0

안녕하세요, 답변 남겨드립니다.

먼저 BWEn의 역할부터 설명드리겠습니다. BWEn(Byte Write Enable)은 말 그대로 Byte 단위 혹은 Bit 단위로 Write 동작을 제어하기 위한 신호입니다. 예컨대 32bit SRAM의 경우 4개의 바이트(8bit × 4)로 구성되어 있고, 각 바이트마다 독립적인 Write Enable 신호를 두어 특정 바이트만 갱신할 수 있도록 합니다. 따라서 질문 주신 것처럼 addr=0일 때 BWEn=11110000이라면, 상위 4bit는 write가 무시되고 하위 4bit만 inner_mem에 반영되는 것이 맞습니다. 즉, 부분 쓰기를 지원하여 불필요한 데이터 손상을 막고, 메모리 버스 활용 효율을 높이는 장치라고 보시면 됩니다. 실제 DRAM이나 Flash Controller에서도 비슷한 Byte Mask 신호가 존재하며, DMA 전송 시 특정 바이트만 갱신할 때 매우 유용하게 쓰입니다.

두 번째 질문인 CSn=WEn=0일 때 동작은 정확하게 이해하고 계십니다. 여러 개의 SRAM 칩이 있을 경우 CSn으로 특정 칩을 선택하고, 해당 칩 내부에서는 주소(addr)를 통해 행(Row)을 선택합니다. 다만 표현하신 “한 행을 선택한다”는 부분을 조금 더 구체화하면, addr 값은 단순히 Row Index가 아니라 Address Decoder를 통해 Word Line을 선택하게 됩니다. 예를 들어 Depth=1024, Width=32bit 구조의 SRAM이라면 addr=0은 “0번째 32bit Word Line”을 선택하고, BWEn을 통해 그 Word 내 일부 바이트만 write하는 구조가 됩니다. 즉, addr=0 → 첫 번째 행(32bit), addr=1 → 두 번째 행(32bit) 순으로 선택이 진행됩니다. 따라서 Row 선택은 맞는 표현이지만, 실제로는 Word 단위 접근으로 이해하시는 것이 더 정확합니다.

세 번째 질문인 inner_mem과 delay에 대해 설명드리면, 보통 RTL 모델링이나 SRAM Behavioral Model에서는 Write Path와 Read Path의 지연 모델링 방식이 다릅니다. Write의 경우, Din → inner_mem 반영에 있어 Clock Edge 기반으로 수행되며, 내부적으로 “Setup/Hold 시간 → Write Cycle Time”을 만족해야 반영됩니다. 따라서 inner_mem이 실제 반영되기까지는 한 클럭의 latency가 발생하는 구조로 모델링되는 경우가 많습니다. 반대로 Read의 경우에는 inner_mem에 저장된 값을 바로 Mux를 통해 Dout으로 전달하는 구조이므로, 클럭 사이클을 기다리지 않고 combinational path처럼 보이게 되는 것입니다. 실제 실리콘 레벨에서도 SRAM의 Read Access Time(tACC)은 Write Cycle Time(tWC)보다 짧거나 유사하게 모델링되며, RTL 단에서는 이를 단순화하기 위해 write는 synchronous, read는 asynchronous 형태로 구현하기도 합니다. 따라서 din → inner_mem은 Clock Sync를 거치며 delay가 발생하고, inner_mem → dout은 combinational path로 모델링되어 바로 값이 출력되는 것처럼 보이는 것이 정상입니다.

추가적으로 Sense Amplifier 관련 질문도 주셨는데, DRAM과 SRAM의 Sense Amp는 유사한 원리(차동 증폭기 구조)를 사용하지만 구현 목적이 조금 다릅니다. DRAM에서는 bitline이 매우 긴 Capacitive Load이므로 미세한 전압 차이를 증폭하기 위해 Sense Amp가 반드시 필요합니다. 즉, 저장된 charge(‘0’/‘1’)를 증폭하여 Full-Swing 전압으로 복원하는 역할을 합니다. 반면 SRAM에서는 Cross-coupled Inverter 구조 자체가 안정적인 전위차를 형성하므로, DRAM처럼 강한 sense operation이 필요하지 않고, 주로 Read Disturb를 최소화하기 위해 Access Transistor와 함께 동작하는 간단한 차동 증폭기를 활용합니다. 즉, 기본 구조는 비슷하지만 DRAM에서는 “데이터 복원 필수 장치”, SRAM에서는 “빠른 판별 및 출력 보조 장치”로 성격이 다르다고 이해하시면 됩니다.

정리하면, BWEn은 부분 쓰기를 위한 Byte Mask 기능이며, addr은 Word Line 선택 신호로서 CSn과 함께 특정 칩·특정 행을 지정하는 역할을 합니다. 또한 inner_mem 동작은 write와 read의 모델링 방식 차이로 인해 delay 여부가 다르게 보이는 것이 맞고, SRAM과 DRAM의 Sense Amp는 원리적으로 유사하지만 쓰임새와 필요성이 다르다는 점에서 차이가 있습니다.

0

추가적으로 BWEn에 대해서 질문드립니다!!

그러면 만약에 addr=0이라고 하면, 0번째 행에 대해서 8bit cell이 선택된다고 가정해보겠습니다. 만약 이때 BWEn=11110000으로 설정하게 되면 상위 4bit는 어떠한 wdata가 들어오던 변경되지 않는다는 의미일까요? 결국 상위 4bit는 차단시키고, 하위 4bit만 저장하게 할 수 있는 그런 장치라고 보면될까요?

조금 다른 추가 질문이지만, 이전에 DRAM 동작 원리 내에서 Sense amp를 공부한적이 있는데 여기서 sense amp가 SRAM에서 사용하는 Sense amp와 같은 구조라고 보면되나요?

0

안녕하세요, 인프런 AI 인턴입니다. ydu343656님.

SRAM의 동작에 대한 질문에 대해 답변 드리겠습니다.

BWEn의 역할:

- BWEn은 Bit Write Enable을 의미하며, 각 비트의 쓰기 가능 여부를 컨트롤합니다. 이는 특정 비트에 대해서만 쓰기를 할 수 있도록 하여 데이터의 부분 수정이 가능하게 해줍니다. 따라서 BWEn는 세밀한 제어를 위해 사용됩니다.

- BWEn은 Bit Write Enable을 의미하며, 각 비트의 쓰기 가능 여부를 컨트롤합니다. 이는 특정 비트에 대해서만 쓰기를 할 수 있도록 하여 데이터의 부분 수정이 가능하게 해줍니다. 따라서 BWEn는 세밀한 제어를 위해 사용됩니다.

CSn, WEn, addr의 동작:

- CSn(Chip Select)은 특정 SRAM 칩을 활성화하는데 사용되고, WEn(Write Enable)은 그 칩 내에서 쓰기를 허용하는 신호입니다. CSn과 WEn 모두 0이어야 해당 칩에서의 데이터 쓰기가 진행됩니다.

- addr은 메모리 내에서의 특정 셀이나 행을 지칭합니다. 여러 개의 SRAM이 있는 시스템에서 각 SRAM 칩은 CSn을 통해 선택되며, addr 값이 해당 칩의 어느 위치를 읽거나 쓸 것인지를 결정합니다. 말씀하신 것처럼, addr=0 설정은 원하는 특정 행이나 셀을 선택하는 역할을 할 수 있습니다.

- CSn(Chip Select)은 특정 SRAM 칩을 활성화하는데 사용되고, WEn(Write Enable)은 그 칩 내에서 쓰기를 허용하는 신호입니다. CSn과 WEn 모두 0이어야 해당 칩에서의 데이터 쓰기가 진행됩니다.

wdata와 rdata의 동작 차이:

- 데이터 쓰기(wdata)와 관련된 딜레이는 작성하는 데이터가 SRAM으로 전송되고 기록되는 시간을 포함하므로 발생합니다.

- 반면, 데이터 읽기(rdata)는 이미 저장된 값을 가져오는 작업이기 때문에 지연이 적을 수 있습니다. 하지만 이는 시스템과 구조에 따라 다를 수 있으며 일반적인 메모리 접근 시간과 아키텍처에 영향을 받습니다.

- 데이터 쓰기(wdata)와 관련된 딜레이는 작성하는 데이터가 SRAM으로 전송되고 기록되는 시간을 포함하므로 발생합니다.

관련하여 이해를 도와줄 수 있는 추가 링크는 없습니다만, 내용이 잘 이해되지 않는 부분에 대한 구체적인 오류나 착각이 있는 것인지 다시 점검해볼 필요가 있습니다.

혹시 더 궁금한 부분이나 설명이 필요하시면 추가 질문해 주세요.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

강의 만료일 연장 신청

0

40

2

강의자료 pdf파일

0

91

2

수강기간변경

0

75

2

프로그램 종류

0

90

1

안녕하세요 강의 도중 궁금한 점 있어서 질문드립니다!

0

87

1

수강기간 변경관련

0

65

2

수강기간 만료

0

72

2

수강 연장 문의

0

72

2

I2C SCL_Synched, SDA_Synched 질문

0

84

1

no data path질문

0

104

3

SRAM 강의 modelsim 시뮬레이션에서 inner 메모리를 Objects 리스트에서 찾으려고 하는데 안보입니다.

0

90

2

DataMem 스펙 질문

0

55

1

Hamming Code 질문

0

68

1

W_CRC 값 질문하기

0

60

1

Precharge에 대한 질문

0

169

1

tpsram spec 질문

0

66

2

학습 관련 질문 있습니다!

0

88

2

[과제7] AXI 통신 프로토콜 설계하기 문의드립니다

0

94

2

SRAM 강의 TB 작성 후 waveform 확인시에 dout이 모두 don't care 처리 관련 질문드립니다.

0

106

5

vivado와 quartus 프로그램의 systhesis 결과 차이에 대해 궁금한 점 있습니다

0

187

2

tool 질문

0

96

2

CDC 메타스태빌리티 질문

0

70

1

SRAM module RTL viewer 이상

0

100

2

slave와 master 시뮬레이션

0

71

2