Xil_In 함수에 관해 질문이 있습니다.

582

작성한 질문수 4

안녕하세요, 해당 강의자료를 참고하여 c code를 작성하고 있습니다. 현재 제가 사용하고 있는 코드의 main 문은 다음과 같습니다.

int main()

{

u32 data;

u32 read_data;

init_platform();

xil_printf("[S/W BUILD]\t%s, %s\n\r",__DATE__, TIME);

xil_printf("[FPGA BUILD]\t%x \n\r",Xil_In32(FPGA_BUILD_ADDR));

xil_printf("--Starting SI5386 init Application--\n\r");

data = 0x00000000;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD, data);

data = 0x00000101;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_INT_STAT, data); // 0x0010

data = 0x00000101;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_INT_EN, data); // 0x0018

data = 0x00093ee0;

data = 0x00023e06;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_TGT_SIZE, data); // 0x0020

data = 0x021c01e0;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PIC_SIZE, data); // 0x0024;

data = 0x000000c4;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PIC_FMT, data); // 0x0028

data = 0x00000000;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PROF, data); // 0x002c

data = 0x00000205;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_NL, data); // 0x0034

data = 0x00000001;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_MODE, data); // 0x0038

data = 0x00000001;

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD, data); // 0x0000

usleep(50);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_INT_STAT);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_INT_EN);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_TGT_SIZE);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PIC_SIZE);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PIC_FMT);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_PROF);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_NL);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_MODE);

read_data = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD);

usleep(50);

cleanup_platform();

return 0;

}

다음과 같이 Xil_Out32 함수가 쭉 써지고, 각각의 메모리 주소에 대해 data를 write 합니다. 이후 해당 주소에 대한 데이터 값을 read 하는 과정에서, hardware에서 인식을 하지 못합니다.

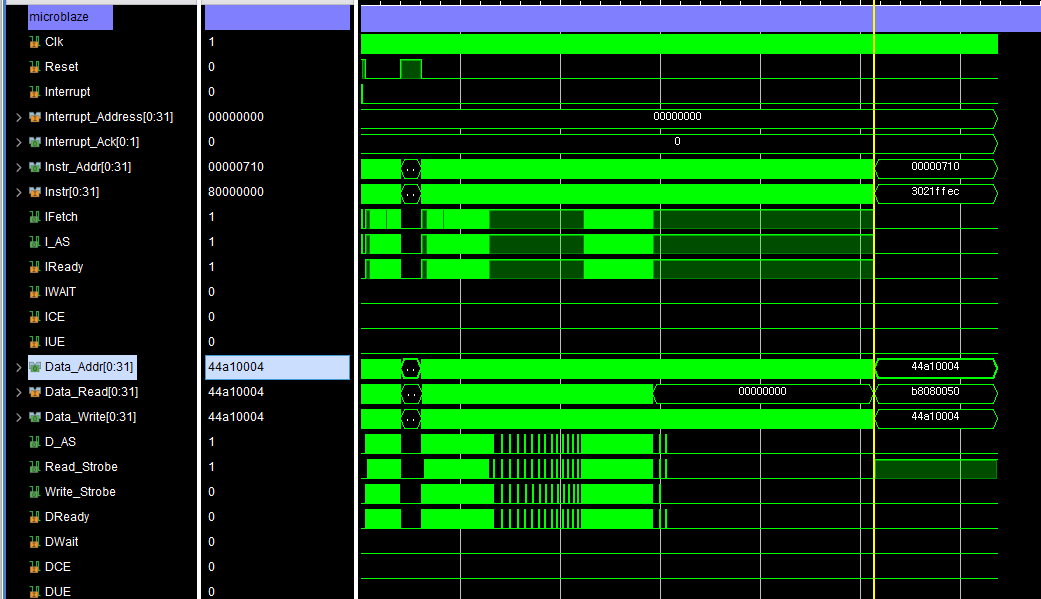

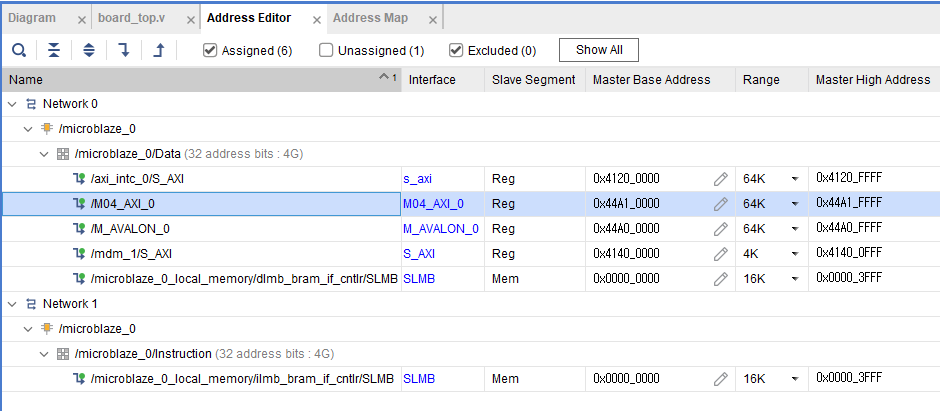

위 사진과 같이, microblaze에서 data address가 첫번째 read 할 주소인 0x44a10004에서 멈춰있는 것을 확인할 수 있습니다.

위 사진과 같이, microblaze에서 data address가 첫번째 read 할 주소인 0x44a10004에서 멈춰있는 것을 확인할 수 있습니다.

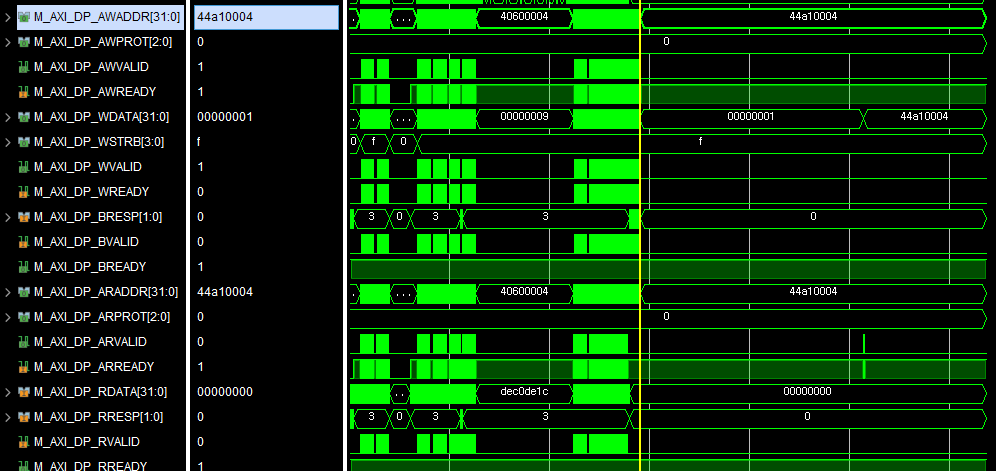

axi쪽 I/F는 다음과 같습니다.

axi쪽 I/F는 다음과 같습니다.

제 C code에서 Read 동작이 되지 않는 이유가 무엇일까요?

감사합니다.

답변 2

0

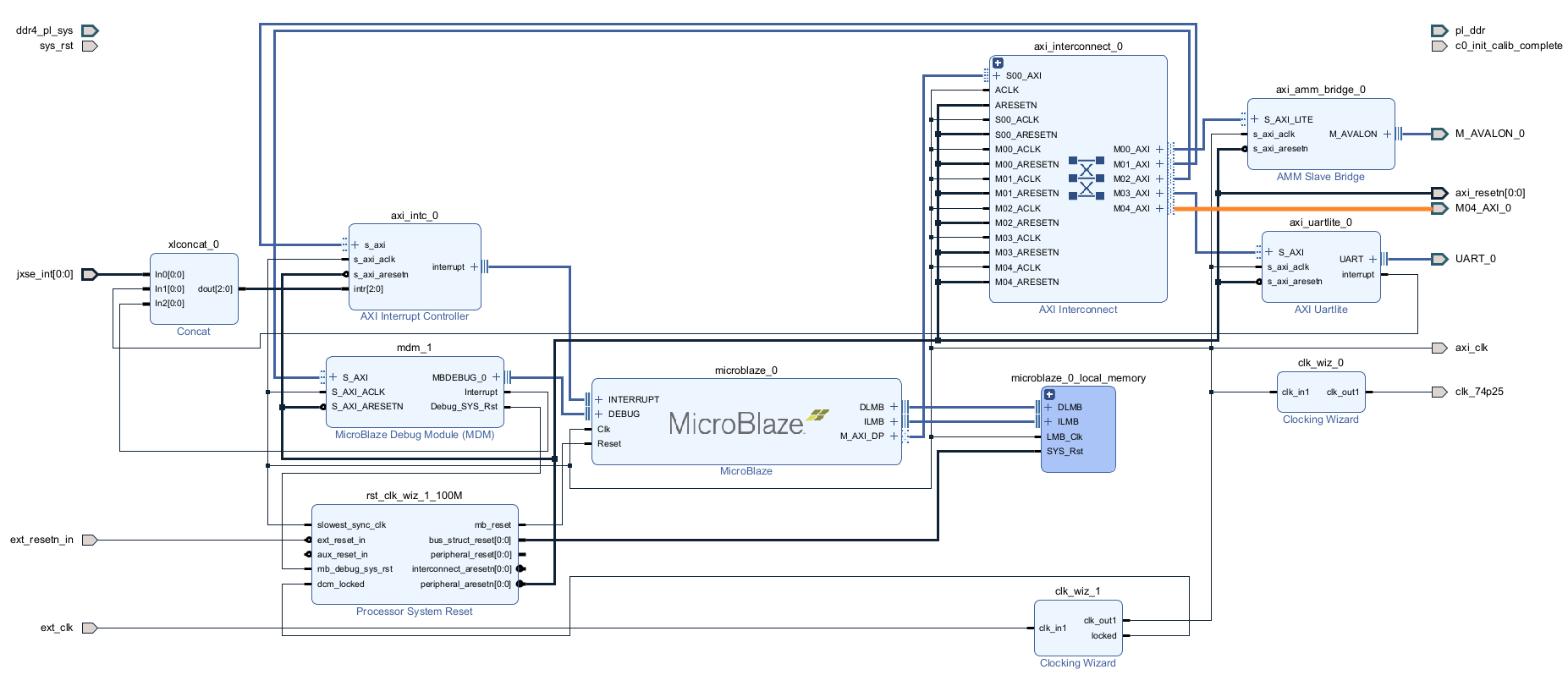

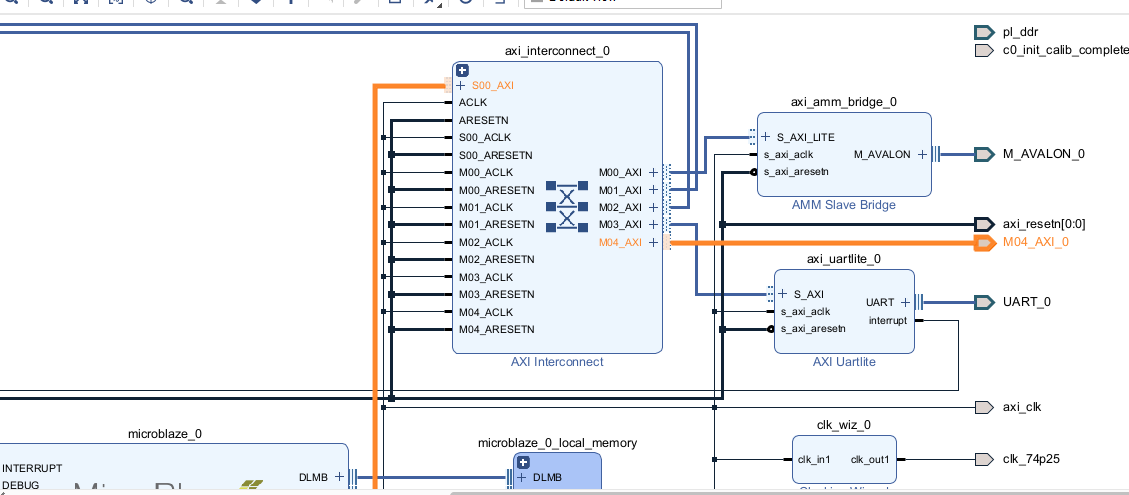

block design은 다음과 같습니다.

Master axi를 하나 더 추가하여(M04_AXI_0) port로 뺀 다음 rtl 상에서 모듈과 연결했습니다.

0

c 코드에 주소값들이 define 상수로 되어 있어서 어떤 값인지 난해하네요.

Xil_Out32(), Xil_In32() 함수 후에 printf 문을 추가하여 디버깅 메시지를 확인해 보시는 게 좋을 것 같네요.

예를 들면,

Xil_Out32(TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD, data);

data = 0x00000101;

xil_printf("out_addr : %X, data : %X \n", TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD, data);

read_data_1 = Xil_In32 (TMC_JXSE_BASE_ADDR + TMC_JXSE_INT_STAT);

xil_printf("out_addr : %X, data : %X \n", TMC_JXSE_BASE_ADDR + TMC_JXSE_ENC_CMD, read_data_1);

c 코드로 넘어 오면, printf 문으로 디버깅하는 것이 좋습니다.

그리고 함수 마지막에 while(1) ; 문을 추가해서 프로그램이 종료되는 것을 막는게 좋을 것 같습니다.

대충 보았을 때에는 특이한 문제가 보이지는 않습니다만,

M04_AX_0 를 추가하는 부분을 한번 더 확인해 보시길 바랍니다. 옵션이나 혹시 잘못된 부분이 있는지 확인해 보세요.

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

32

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

33

2

queue assignment pattern 문의 건

0

33

1

Mission 5 문의 건

0

46

2

Zynq z7 FPGA single-ended 관련

0

40

1

강의자료 PDF 어떻게받나요?

0

42

2

Differential Amp의 4가지 종류

0

41

1

[HDL 22장] F/F CE 관련 질문

1

46

2

UART0, 1 중 선택

1

51

2

fpga 개발보드

0

29

2

vivado 2022.1 version memory IP 구조

0

38

1

강의 ppt 자료 요청건

0

56

2

Block Memory Interface 응용

0

349

1

수업 내용중 질문드립니다.

0

382

1

수업 자료 링크 오류

0

229

1

xdc파일 핀할당에 대해 문의드립니다.

0

411

1

lwip echo server ping test 문의 드립니다.

0

432

1

W5500코드 관련 질문

0

354

1

w5500

0

354

1

자료링크 "접근이 불가능합니다"

1

265

1

한 페이지가 안보입니다.

1

296

1