안녕하세요 삼코치님 정성껏 만들어주신 강의 듣고있는 수강생 입니다.

다름이아니라 3년 이상 경력직 전장설계 공고에 서류합격을 하였으나 PT면접 내용(회로/배선 설계시의 중요 체크포인트를 주제로 10분간 발표로 공지됨) 구성에 어떻게 강점을 줄지 고민이 되어 문의 드립니다.

현재 프로젝트 계약직으로 재직중인 회사에서 HW팀 연구원으로 2년 6개월 가량 근무중에 있으나, 주 업무 범위는 제가 담당하는 장비의 HW요구사항 도출/HW 아키텍처,레이아웃 설계/사양서 작성/시험 및 검증 업무 등으로 되어있고

주장비 내에 들어가는 전원분배장치(전원분배/제어 모듈) 내부 보드의 회로도면은 있지만 설계 및 제작은 협력사에서 진행하여 실무간 직접 회로설계 경험이 없기에 삼코치님 강의를 시작으로 개인 프로젝트를 준비하는 초창기 단계였습니다,

이런 상황에서, PT 발표의 구성을 아래의 구성느낌으로 가져 가려고 하는데, 괜찮으시다면 삼코치님께 피드백을 요청드립니다. (아직 많이 초보 단계인점 양해 부탁드립니다ㅠ.ㅜ)

PT발표 주제 : 회로/배선 설계시의 중요 체크포인트 (10분 발표)

목차

1.전원 설계 체크포인트

고전류(모터) / 저전압(제어) 전원 분리

돌입전류 대응 여부 (실무간 설계 오류 사례 공유)

역극성·과전압 보호 회로

2.신호·통신 설계 체크포인트

센서 입력 레벨 매칭

Pull-up / Pull-down 적정성

아날로그·디지털 신호 분리

모터 구동 노이즈 영향 검토

3.배선·하네스 설계 체크포인트

전력선 / 통신선 분리

병렬 배선 최소화, 교차 시 90도

차폐선 접지 기준 명확화

진동 대응 Lock 구조 커넥터

오결선 방지(Keying) 설계

하네스 여유 길이 및 정비성 고려

4.환경·신뢰성 설계 체크포인트

온도 변화에 따른 전압·센서 오차

습기·먼지에 의한 누설·접촉 불량

단선, 통신 끊김 시를 대비한 이중화 구조

5.소자 선정시 체크포인트

MCU CPU/메모리등 성능, 주변장치 구성, 전력소모등 고려

커패시터 선정간 고려사항(정격전압, 정전용량 , 용도 등)

시간 여유있으실때 한번 검토해주시면 정말 감사드리겠습니다!

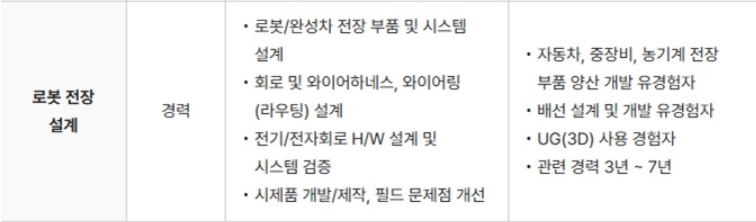

참고가 될까하여 아래 지원한 공고의 JD 캡쳐본 올려드립니다.

안녕하세요, 답변 남겨드립니다.

올려주신 목차는 방향이 좋습니다. 다만 JD가 요구하는 포인트가 “회로 자체를 그리는 능력” 하나로만 평가되지 않고, 로봇/완성차 전장 관점에서 시스템 설계와 하네스/와이어링 라우팅, 그리고 검증과 필드 이슈 개선까지 포함되어 있기 때문에, 10분 PT에서는 체크포인트를 많이 나열하기보다 “장애가 나는 메커니즘을 정량으로 설명하고, 그걸 설계 산출물과 검증 항목으로 어떻게 닫는지”를 보여주시는 쪽이 더 강점이 됩니다. 질문자님은 요구사항 도출, HW 아키텍처, 레이아웃, 사양서, 시험/검증 경험이 있으시므로, 회로 설계 직접 경험이 상대적으로 적다는 점을 약점으로 두기보다는 “협력사 설계라도 내가 시스템 관점에서 리뷰하고 검증으로 품질을 보증한다”는 강점으로 전환하시는 구성이 유리합니다.

발표 흐름은 도입에서 지원 직무의 핵심을 한 문장으로 정리하고, 본론에서는 전장 고장 경로를 전원 무결성, 신호 무결성/EMC, 인터커넥트(하네스/커넥터) 신뢰성의 세 축으로 잡은 뒤, 각 축마다 대표 사례 1개씩을 깊게 파고드는 형태가 가장 안전합니다. 10분 기준으로 도입 1분, 본론 8분, 마무리 1분 정도로 가져가시면 질의응답에서도 흔들리지 않습니다. 이때 “체크포인트”를 말로만 선언하지 마시고, 각 파트에 최소 1개의 숫자 기준과 1개의 계산식, 그리고 1개의 측정/검증 방법을 붙이시면 경력직 면접에서 체감 점수가 크게 올라갑니다.

전원 설계는 지금 적어주신 고전류/저전압 분리, 돌입전류, 역극성·과전압 보호를 그대로 쓰시되, 분리를 “물리적 분리 + 전원 트리 분기점 관리 + 리턴패스 관리”로 구체화해주시는 게 좋습니다. 예를 들어 24 V 입력 장비에서 모터 드라이버가 기동 순간 10 A 피크를 만들고, 제어계가 3.3 V에서 0.5 A를 소비한다고 가정하면, 하네스 왕복 저항이 40 mΩ만 되어도 전압 강하는 Vdrop = I * R = 10 A * 0.04 ohm = 0.4 V가 즉시 생깁니다. 여기에 커넥터 접촉저항, 퓨즈, 입력 필터 ESR까지 더해지면 드룹이 0.6 V 이상으로 커질 수 있고, 이때 DC/DC의 UVLO나 MCU BOR 임계치와 겹치면 “모터 기동 시 리셋”이 아주 전형적으로 발생합니다. 이 사례 하나만 잡고, 해결을 “입력단 에너지 저장 + 컨버터 UVLO/BOR 설정 + 전력 루프 최소화 + 제어계 분기점 분리”로 닫으시면 됩니다. 홀드업은 I = C * dV/dt에서 C = I * dt / dV로 바로 계산이 가능하니, 예를 들어 3.3 V 레일에서 0.5 A를 5 ms 동안 버티고 허용 드룹을 0.3 V로 잡으면 C = 0.5 * 0.005 / 0.3 = 0.0083 F, 즉 8300 uF 급이 나와서 “보드에 무작정 커패시터를 키우는 접근은 비현실적이고, 24 V 입력단에서의 에너지 관리와 시퀀싱이 같이 가야 한다”는 결론이 자연스럽게 나옵니다. 돌입전류는 반대로 I_inrush ≈ C * dV/dt로 설명하시고, 커패시터 증설이 곧바로 inrush 증가로 이어져 스위치/퓨즈/커넥터에 스트레스를 준다는 점을 짚은 다음, 소프트스타트, 핫스왑, NTC, 또는 프리차지 저항+바이패스 같은 대응을 한 가지로 정리해주시면 됩니다. 역극성 보호는 아이디얼 다이오드 방식 MOSFET을 예로 들면서, 손실을 P = I^2 * Rds_on으로 정량화하시면 좋습니다. 예를 들어 10 A에서 Rds_on이 5 mΩ면 P = 10^2 * 0.005 = 0.5 W라서 발열/방열 설계가 곧바로 논리적으로 연결됩니다. 과전압 보호는 TVS를 예로 들어 “클램프 전압이 후단 DC/DC의 Abs Max보다 충분히 낮아야 하고, 펄스 조건에서의 Ipp/에너지 허용치를 만족해야 한다”를 선정 원칙으로 말씀하시면 회로를 직접 그렸는지와 무관하게 설계 판단 능력이 드러납니다. 검증은 오실로스코프로 부하 스텝(예: 0 A에서 10 A로) 시 24 V 버스와 3.3 V 레일의 최소전압, 드룹 지속시간(ms), 링잉 크기(Vpp)를 측정해 “통과 기준”을 제시하시는 방식이 가장 설득력 있습니다.

신호·통신은 센서 입력 레벨 매칭과 Pull-up/Pull-down을 단순 나열하지 마시고, “요구 사양을 전기적 한계로 변환한다”를 보여주시는 게 포인트입니다. I2C 같은 오픈드레인 예시로 버스 캐패시턴스 Cbus = 200 pF, 목표 rise time tr = 300 ns를 가정하면 Rp_max ≈ tr / (0.8473 * Cbus)로 Rp_max ≈ 300e-9 / (0.8473 * 200e-12) ≈ 1.77 kohm가 나옵니다. 즉 2.2 kohm을 쓰면 상승시간이 느려져 마진이 줄 수 있고, 1.5 kohm으로 내리면 로우레벨 싱크 전류가 커져 드라이버 능력과 소비전류가 불리해진다는 트레이드오프를 숫자로 설명할 수 있습니다. 통신이 CAN이라면 종단 120 ohm, 스텁 길이 제한, 커먼모드 초크/ESD 보호, 리턴패스 연속성 같은 항목으로 “노이즈 환경에서 통신 에러율을 어떻게 줄이는지”를 말할 수 있고, 면접관이 전장 출신이면 이쪽을 더 좋아하는 경우가 많습니다. 아날로그·디지털 분리는 “그라운드를 쪼갠다”로 가면 오히려 역효과가 날 수 있어서, “민감한 아날로그 리턴이 모터 전력 리턴과 공유되지 않도록 전류 경로를 설계하고, ADC 입력은 RC 필터와 레이아웃으로 방어한다”로 표현하시는 게 안전합니다. 예를 들어 센서 출력이 0~3.3 V이고 원하는 대역이 100 Hz라면, 간단히 fc = 1/(2piR*C)로 잡아 R = 1 kohm, C = 1.6 uF면 fc ≈ 100 Hz가 되어 고주파 노이즈를 줄일 수 있다는 식의 정량 예시를 넣으시면 “체크포인트”가 “설계 판단”으로 바뀝니다. 모터 구동 노이즈는 스위칭 노드 면적 최소화, 파워 루프/게이트 루프 면적 최소화, 고 di/dt 경로와 센서/통신 라인의 물리적 거리 확보, 그리고 무엇보다 연속 GND plane 위로 신호를 라우팅해 리턴패스를 끊지 않는다는 원칙을 한 문장으로 강하게 가져가시면 됩니다.

배선·하네스는 JD에서 직접적으로 요구하는 영역이므로, 여기서 점수를 가장 크게 벌 수 있습니다. 전력선/통신선 분리는 단순 분리보다 “전압강하 예산, 발열, EMC”로 프레임을 잡아주시는 게 좋습니다. 예를 들어 5 m 하네스에서 10 A를 공급해야 하고 도체 저항이 10 mΩ/m(왕복이면 2배) 수준이라고 가정하면, Vdrop = 2 * L * R_per_m * I = 2 * 5 * 0.01 * 10 = 1.0 V가 나옵니다. 24 V 시스템에서는 허용될 수도 있지만, 모터 드라이버의 저전압 보호나 토크 성능에 영향을 줄 수 있으니 “허용 전압강하를 3%로 잡으면 24 V 기준 0.72 V 이하가 목표”처럼 목표를 세우고, 그에 맞춰 선경(AWG), 분기 구조, 접점 수(병렬 핀), 커넥터 정격을 결정한다고 말하시면 설계가 굉장히 현업적으로 들립니다. 커넥터는 Lock, Keying, 오결선 방지까지 이미 잘 잡으셨고, 여기에 접촉저항 증가가 발열로 이어진다는 점을 P = I^2 * R로 한 번만 찍어주시면 강해집니다. 예를 들어 접촉저항이 열화로 5 mΩ 증가했을 때 10 A면 0.5 W가 커넥터 한 점에서 발생하므로, 진동 환경에서는 “락 구조+스트레인 릴리프+핀당 전류 디레이팅”이 왜 필요한지가 즉시 설명됩니다. 차폐선 접지는 “저주파에서는 루프전류를 막기 위해 단일 접지, 고주파에서는 차폐 연속성을 위해 커넥터에서 360도 접속 및 섀시 접지”처럼 주파수 관점으로 정리하시면 논리성이 생깁니다. 라우팅은 UG(3D) 같은 툴 경험이 있으면 언급하되, 없더라도 “3D 간섭 검토, 최소 굴곡 반경, 서비스 루프(정비 여유), 클립/브라켓 위치, 모서리 마찰 보호”를 요구사항과 연계해 설계한다는 식으로 말하시면 충분히 커버됩니다.

환경·신뢰성은 나열형에서 “오차 예산과 고장 안전”으로 바꾸시면 좋습니다. 온도 변화에 따른 센서 오차는 데이터시트의 tempco를 기준으로 시스템 요구 정확도(예: ±1.0%FS)에서 센서, ADC, 레퍼런스, 배선/EMI로 오차를 배분하는 방식으로 접근하시면 설계자 관점이 드러납니다. 습기·먼지는 누설전류를 정량으로 보여주시면 임팩트가 큽니다. 예를 들어 고임피던스 입력에서 Rin = 100 kohm이고 누설전류 Ileak = 100 nA만 생겨도 Verror = Ileak * Rin = 10 mV가 되어, 12-bit ADC(3.3 V 기준 LSB ≈ 0.8 mV)에서는 12 LSB 이상 오차가 될 수 있으니, 코팅/가드링/입력 임피던스 설계/클리닝 공정이 왜 중요한지가 한 번에 설명됩니다. 단선, 통신 끊김 대비는 “이중화”를 말하기 전에 “Fail-safe 상태 정의”가 먼저입니다. 예를 들어 통신 타임아웃 100 ms를 넘으면 모터 출력 0%로 내리고, 센서 단선 감지 시 마지막값 유지가 아니라 제한값으로 클램프한다는 식으로, 숫자와 동작을 한 문장으로 박아주시면 현업에서 통하는 답이 됩니다.

소자 선정은 MCU와 커패시터를 적으신 것이 기본은 맞지만, 발표에서는 “선정 원칙”이 더 중요합니다. MCU는 CPU/메모리만 말하면 임베디드 면접처럼 들릴 수 있으니, 전장에서는 주변장치 매칭과 리스크로 정리하시는 게 좋습니다. 예를 들어 필요한 통신(CAN/LIN/RS-485), 타이머 해상도(PWM 주파수와 분해능), ADC 채널 수/샘플링/동시샘플 필요 여부, watchdog, 부트 업데이트 전략, BOR 설정 가능 여부 등을 요구사항과 연결하시면 설득력이 높습니다. 커패시터는 정격전압/정전용량 외에도 DC bias로 유효용량이 감소하는 문제, ESR/리플전류 정격, 온도 특성을 언급하시고, “레일별 최소 유효용량을 기준으로 병렬 분산 배치하고, 전원부는 리플전류 정격을 만족하는 부품을 쓴다”로 닫으시면 됩니다. 여기서도 숫자가 있으면 더 좋고, 예를 들어 스위칭 레귤레이터 출력 리플 목표가 20 mVpp라면 허용 임피던스 목표를 Z_target = Vripple / I_ripple로 잡아 부품 ESR과 레이아웃 임피던스를 같이 관리한다는 식으로 말씀하시면 설계 품질 관점이 선명해집니다.

마무리는 “내가 실제로 현업에서 무엇을 남기는 사람인지”로 끝내시는 것이 좋습니다. 협력사가 회로를 설계하더라도, 질문자님은 요구사항을 전기적 수치로 변환하고, 회로/레이아웃/하네스 설계를 리뷰 체크리스트로 관리하며, DVP에 전원 부하 스텝, 리셋 재현, 통신 에러율, 진동 후 접촉불량, 온도 사이클 후 센서 오차 같은 시험 항목을 설계 체크포인트와 1:1로 매핑해 필드 이슈를 줄여왔다고 정리하시면, JD의 “시스템 검증, 시제품 개발/제작, 필드 문제점 개선”과 정확히 맞물립니다. 이런 구성으로 가시면 회로를 직접 그린 양이 많지 않아도, 경력직 전장설계에서 요구하는 “품질을 닫는 사람”으로 강하게 보이실 가능성이 높습니다.

답글