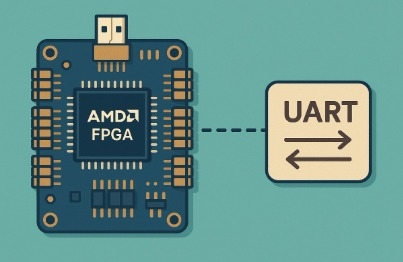

Triển khai UART trên FPGA

UART là một phương thức giao tiếp nối tiếp cơ bản và được sử dụng rộng rãi, là một chủ đề học tập rất phù hợp cho người mới bắt đầu tiếp cận thiết kế FPGA. Trong khóa học này, chúng ta sẽ tìm hiểu chi tiết về nguyên lý giao tiếp và cấu trúc khung của UART, sau đó tiến hành quá trình tự triển khai logic truyền nhận thông qua thiết kế RTL (Register Transfer Level) dựa trên hiểu biết đó. Bằng cách triển khai UART trên FPGA, bạn có thể phát triển một cách có hệ thống năng lực thiết kế mạch kỹ thuật số và tích lũy kinh nghiệm kiểm tra hoạt động ở cấp độ phần cứng thực tế thông qua mô phỏng và kiểm định. Ngoài ra, bạn cũng sẽ học cách sử dụng Soft Processor như MicroBlaze và Xilinx UART IP, từ đó hiểu rộng hơn về quy trình thiết kế hệ thống dựa trên bộ xử lý và cấu hình giao diện. Qua đó, bạn có thể trang bị năng lực phát triển toàn diện, bao gồm cả thiết kế logic và thiết kế bộ xử lý.

36 học viên

Độ khó Cơ bản

Thời gian Không giới hạn

- Đã giải quyết

Zybo 환경에서 PL RTL UART 보드 검증 방법

안녕하세요, 강의 수강 중 문의드립니다. * 저는 아직 이해가 부족한 부분이 많아 질문 내용을 AI의 도움을 받아 정리하였습니다.<p

fpgasystem-veriloguartvivadomini9136

・

15 ngày trước

0

31

2

- Chưa giải quyết

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다.

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다. 아님 맨처음에 설정에서 보드 설정이 있는데 그걸로도 가능한지 궁금합니다.

fpgasystem-veriloguartvivadolemmon78198028

・

2 tháng trước

0

63

1

- Đã giải quyết

5장 강의 노트 확인 부탁드립니다.

5. UART TX/RX 모듈 RTL 설계 및 시뮬레이션강좌의 강의 자료를 다운 받으면 ep06_Intergration 자료 입니다.확인 부탁드립니다.</

fpgasystem-veriloguartvivadoinair3292

・

7 tháng trước

0

68

2

- Đã giải quyết

RTL

RTL이 Veliog인거같은데 vhdl 버전은 없나요 ?

fpgasystem-veriloguartvivadoflak397306

・

8 tháng trước

0

98

1

- Đã giải quyết

멀티바이트프레임 로직 예시

FIFO를 이용하여 멀티바이트프레임 로직 구문을 작성 및 처리하는 참조 할 만한 로직 예시 가 있을까요

fpgasystem-veriloguartvivadojookd787339

・

8 tháng trước

0

90

2