시뮬레이션 타이밍 관련 질문있습니다.

391

3 câu hỏi đã được viết

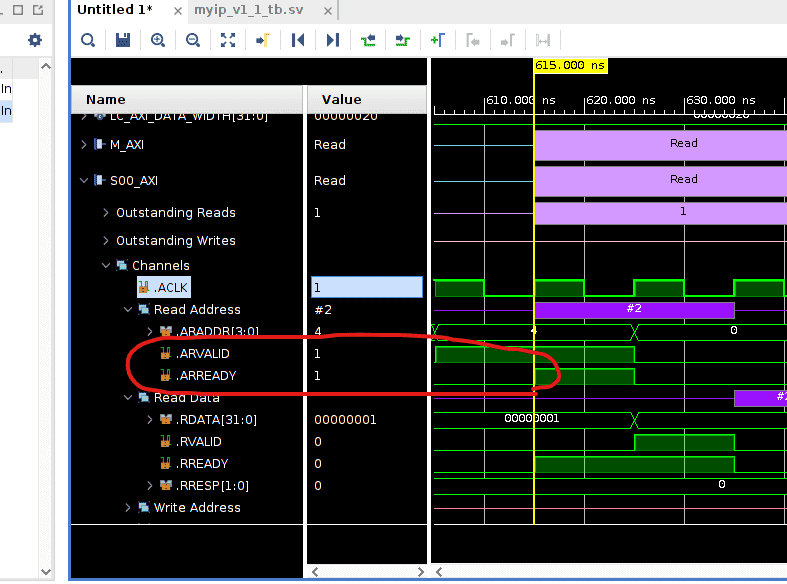

그림과 같이 clk posedge에서 READ ADRESS channel에서ARREADY의 값이 1인데 ARREADY는 reg 하고 연결이 되어있으니까 rising time을 고려하면 0으로 인식되어야하는게 아닌가요? 시뮬레이션이여서 이런 환경은 배제해야되는 건가요?

Câu trả lời 2

1

안녕하세요 :)

그림과 같이 clk posedge에서 READ ADRESS channel에서ARREADY의 값이 1인데 ARREADY는 reg 하고 연결이 되어있으니까 rising time을 고려하면 0으로 인식되어야하는게 아닌가요?

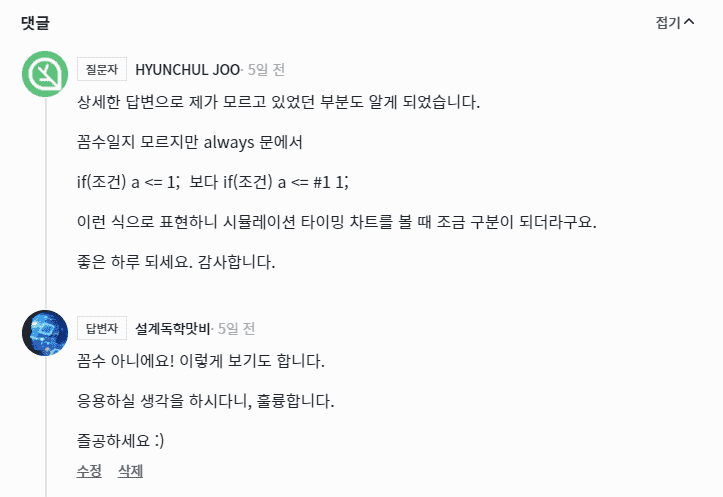

어느 시점에 rising time 을 고려하는지를 모르겠으나, 올려주신 그림의 615 ns 기준이라면 '1' 로 인식을 합니다. (0 -> 1 로의 transition이지만 delay가 고려안된 functional sim 이라서)

시뮬레이션이여서 이런 환경은 배제해야되는 건가요?

delay 가 없는 환경이기 때문에(function sim), 클럭 rising edge 순간에 판단 대상이 되는 신호도 함께 transition 이 됩니다.

실제 현업 (저는 잘 안쓰지만) + 질문자 님들도 해당 방법을 통해서 simulation 을 보시구요.

좋은 방법이라 생각합니다.

다른 분들의 질의응답도 조금이나마 도움이 되실까하여 링크로 남겨드립니다.

그럼 즐공하세요 :)

UART0, 1 중 선택

1

51

2

datamoverbram모듈질문

1

63

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

85

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

71

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

292

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

150

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

152

2

9장 LED 점등 안됨

1

110

3

Edit in IP Packager 이후에

1

83

1

Fpga 로직

1

89

2

pmu-fw is not running

1

127

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2