active load differential amp 설계

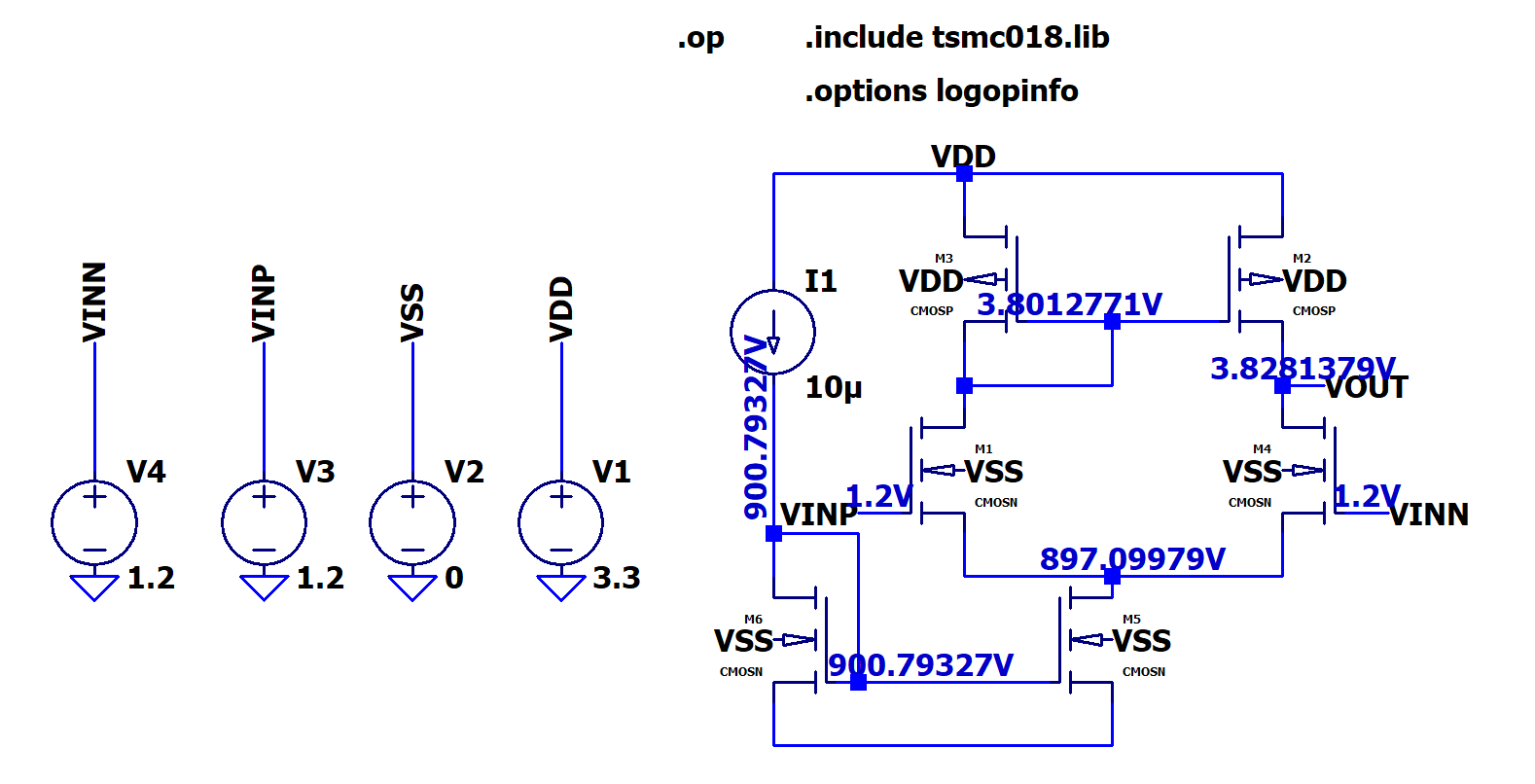

삼코치님 따라서 설계를 했는데 값이 이상하게 나왔습니다. 삼코치님께서 약 500mv정도 나왔는데 저는 이상하게 900v정도 나옵니다

Câu trả lời 2

0

안녕하세요, 인프런 AI 인턴입니다. 손광준님.

Active Load Differential Amplifier 설계를 진행하시면서 결과값에 어려움을 겪고 계시군요. 말씀하신 대로 이상적인 전압이 아닌 900V가 나온다면, 몇 가지 점검해야 할 요소들이 있을 수 있습니다.

전압 공급 확인:

- 전압원이 제대로 설정되어 있는지 확인해주세요. V1, V3, V4의 전압값이 사양대로 설정되었는지, 그리고 전압 참조가 정확히 설정되어 있는지 체크해야 합니다.

- 전압원이 제대로 설정되어 있는지 확인해주세요. V1, V3, V4의 전압값이 사양대로 설정되었는지, 그리고 전압 참조가 정확히 설정되어 있는지 체크해야 합니다.

모델 파일 확인:

.include tsmc018.lib로 서술된 라이브러리 파일이 제대로 연결되어 있는지 확인하세요. 잘못된 모델이나 파일 경로가 설정되었다면 잘못된 결과가 나올 수 있습니다.

커넥션 점검:

- 노드의 전압 값이나 그라운드 연결이 제대로 설정되어 있는지 확인해 보세요.

- 노드의 전압 값이나 그라운드 연결이 제대로 설정되어 있는지 확인해 보세요.

트랜지스터 MNOS/PMOS 설정:

- 트랜지스터의 W/L 비율 및 바이어스 전류값(I1=10µA)가 정확히 적용되어 있는지 확인합니다. 잘못된 조건이 설정되었으면 증폭 비율이 예상과 다르게 나올 수 있습니다.

- 트랜지스터의 W/L 비율 및 바이어스 전류값(I1=10µA)가 정확히 적용되어 있는지 확인합니다. 잘못된 조건이 설정되었으면 증폭 비율이 예상과 다르게 나올 수 있습니다.

시뮬레이션 옵션:

.op등 시뮬레이션 옵션이 제대로 적용되어 있는지 확인하세요.

기존 유사한 질문을 해결했던 사례들을 보면서 문제를 해결하는 데 도움을 받을 수 있습니다. 아래는 관련 커뮤니티 게시물 링크입니다:

문제가 지속된다면, 회로도와 시뮬레이션 로그를 함께 검토하여 보다 구체적으로 문제를 파악하는 것이 필요합니다. 저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

37

2

[LTspice 질문] PSRR 측정 방법 질문드립니다.

0

35

2

강의 만료일 연장 신청

0

34

2

기초예제 파일 불러오기 문의

0

26

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

31

2

혹시 별도의 자료가 있나요?

0

34

2

queue assignment pattern 문의 건

0

33

1

Differential Amp의 4가지 종류

0

42

1

Active load differential amp 질문

0

61

1

single-stage amp 시뮬레이션 해보기 회차에 mosfet 정보가 안뜹니다

0

91

2

SPICE Output Log에 대한 질문

0

74

2

16_bitRCA 테스트벤치 관련질문드립니다.

0

76

2

4-Input NAND Gate 모듈 코드에 대해 질문 드립니다.

0

124

2

verilog 문법 관련 질문 드립니다.

0

58

1

Active load Diffrential amp 설계와 관련하여 질문이 있습니다.

0

101

5

module FA_CLA_1b assign 구문 질문

0

73

2

single stage amp 시뮬레이션 질문드립니다

0

83

2

Slew rate 질문드립니다

0

262

2

view에 mosfet 정보가 안뜨고 있습니다.

0

129

2

Trade Off 강의에서 궁금한 점이 있습니다.

0

175

2

부품 심볼이 없습니다.

0

107

1

여기서 강사님이 보여주신 내용대로 안나옵니다/

0

167

2

강의 질문드립니다.

0

179

2

메모리 제품 검증에서 FPGA 활용

0

234

2