이력 사항

現) 반도체 대기업 (CHIP 회로설계 4년차)

아날로그 IP / 디지털 시나리오 설계

A급 특허 출원

글로벌 외국 기업 엔지니어 기술 대응

前) 스타트업 인큐베이팅 업체 (MCU Firm-ware 설계)

前) 대기업 가전제품 업체 (All-in-one 정수기 생산 기술)

前) 중견기업 의료기기 업체 (CIS, DDI ASIC 설계)

CHIP 설계 취업/이직 충분히 도전할 수 있습니다.

저와 함께 CHIP 설계 취업/이직에 가까워지세요!

"반도체 아날로그/디지털 회로설계를 꿈꾸시나요?

대기업 S전자 현직자의 눈으로 기초부터 도와드립니다!"

반갑습니다! S전자에서 시스템반도체를 설계하고 있는 삼코치 입니다 :)

저는 스타트업에서부터 회로설계 직무에 도전하면서 많은 시행착오를 겪어왔습니다.

PCB 설계, F/W 설계, FPGA 설계, CHIP 설계를 구먹구구 식으로 경험했죠.

그런데 한 가지 아쉬움이 있었습니다.

'왜 회로설계 분야는 체계화된 실습 기회와 취업에 대한 정보가 적을까?'

반도체 공정, 프로그래밍 등의 분야는 콘텐츠가 많았지만, 회로설계는 정보가 적다보니 그저 '숨겨진 세상'이었습니다.

이 글을 읽는 회로설계 취준생분들 또한 저와 같은 답답한 심정을 느껴보셨을 겁니다.

그래서 현직자와 면담도 해보고, 교수님께 물어보고, IDEC 강의를 수강해보기도 하죠.

하지만 알들말듯 여전히 잘 모르는 경우가 대부분 입니다.

그.래.서! 제가 직접 취업까지 연결되는 체계화된 강의를 제작해 버렸습니다!

저는 [아날로그 회로-> 디지털 시스템 -> MCU 펌웨어 -> 드라이버 설계 -> 소프트웨어]를 모두 경험하면서,

'Top-down / Bottom-up'스킬을 통해 제품과 회로를 완벽히 설명해낼 수 있게 되었습니다.

그리고 인프런에서 실무적인 회로를 다루면서 '아날로그/디지털 회로'에 대해 저만의 직관적 해석 방법부터 Trade-off를 따지는 방법까지 모두 풀어드리려 합니다.

저와 함께 기초를 닦고, 실무 역량을 쌓아 자신만의 Chip 설계 Story를 만들어 가봅시다!

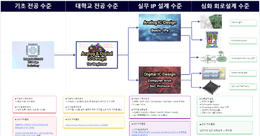

강의

로드맵

전체 1수강평

- PCB HW설계 실무 : STM32를 활용한 Mixed-signal 보드 설계 프로젝트

- PCB HW설계 실무 : STM32를 활용한 Mixed-signal 보드 설계 프로젝트

- 디지털 회로설계 실무 : Computer Architecture 와 SoC 프로토콜 Digital IP 설계하기

- 디지털 회로설계 실무 : Computer Architecture 와 SoC 프로토콜 Digital IP 설계하기

- 아날로그 회로설계 실무 : Analog IP 설계와 성능 개선하기

게시글

질문&답변

Precharge에 대한 질문

안녕하세요, 답변 남겨드립니다.질문 주신 Write 동작 후 Precharge 단계의 필요성은 DRAM의 구조적 특성과 인터페이스 동작 방식 때문에 반드시 요구됩니다. 말씀하신 것처럼 Write 시에 비트라인 쌍(Bitline pair, BL/BLB) 중 선택된 셀은 Write Driver가 강하게 값을 밀어 넣어 저장 캐패시터에 ‘1’ 혹은 ‘0’이 충전됩니다. 이 시점만 놓고 보면 원하는 데이터가 셀 내부에 이미 안정적으로 기록된 것처럼 보이기 때문에 추가적인 동작이 필요 없어 보일 수 있습니다. 그러나 실제 DRAM 구조에서는 다음과 같은 이유로 Write 이후에도 Precharge 과정이 요구됩니다.첫째, 비트라인 전압의 불균형 문제 때문입니다. Write 동작 시 Write Driver는 BL과 BLB 중 하나를 Vdd 가까이로, 다른 하나를 GND 가까이로 강하게 밀어 넣습니다. 이렇게 하면 셀은 원하는 데이터로 기록되지만, 액세스가 끝난 시점에서 비트라인 쌍은 여전히 한쪽은 Vdd, 다른 쪽은 0V에 가깝게 불균형 상태로 남아 있습니다. DRAM의 Sense Amplifier 및 차후 Access 동작은 BL/BLB가 동일한 기준 전압(Vdd/2)에서 시작해야 정확히 동작하기 때문에, Precharge 과정이 필요합니다. Precharge 회로는 BL과 BLB를 모두 Vdd/2로 equalize 해주어 다음 Access의 초기 조건을 만족시킵니다.둘째, Row 간 독립적인 접근을 위해서입니다. 하나의 Wordline을 비활성화한 후 바로 다른 Wordline을 활성화하려면, 공통 비트라인에 남아있는 이전 데이터의 전압 레벨이 제거되어야 합니다. 만약 Precharge 없이 곧바로 다른 Row를 열면, 새로운 셀에서 전달되는 미세한 전하(수 fF 수준)가 기존 Write 시 남아있던 비트라인 전압 차에 묻혀버려 Sense Amplifier가 올바른 판단을 하지 못할 수 있습니다. 따라서 DRAM 아키텍처에서는 “ACT → R/W → PRE”의 순서를 기본 Cycle로 정의하고, 각 단계가 끝날 때마다 비트라인을 초기화하는 과정을 필수적으로 거칩니다.셋째, 실제 DRAM 타이밍 파라미터 관점에서도 Precharge는 Write 동작 후에 반드시 고려됩니다. 대표적으로 tWR(Write Recovery Time)과 tRP(Precharge Time)이라는 지연 시간이 정의되어 있습니다. 예를 들어 DDR3-1600에서 tWR은 약 15ns, tRP는 13.75ns 정도인데, 이는 Write 후 데이터가 Sense Amp에서 셀에 안정적으로 저장되고 난 뒤 Precharge가 완료되기까지 필요한 시간입니다. 서버용 DRAM에서는 이 두 파라미터를 합쳐 최소 수십 ns 단위의 지연이 발생합니다. 즉, 메모리 컨트롤러 차원에서도 Precharge는 Write 사이클의 필수 요소로 인식되고 타이밍 제약에 반영됩니다.현업 예시를 들어보면, 삼성전자 DDR5 DRAM 컨트롤러 설계에서는 Write 동작 후 “Auto-Precharge” 옵션을 사용하여 컨트롤러가 별도의 Precharge 명령을 내리지 않아도 내부적으로 비트라인이 자동 초기화되도록 FSM을 설계합니다. 이 기능은 메모리 채널 효율을 높이는 핵심 기법인데, 그만큼 Precharge가 Write 후에도 빠질 수 없는 단계라는 의미입니다.정리하면, Write 후에도 Precharge가 필요한 이유는 첫째, 비트라인 쌍을 다시 기준 전압(Vdd/2)으로 equalize하여 Sense Amplifier의 동작 조건을 만족시키기 위함이고, 둘째, Row-to-Row 간 간섭을 방지하기 위해서이며, 셋째, JEDEC DRAM 표준 타이밍 제약에도 반드시 포함되기 때문입니다. 따라서 단순히 셀에 데이터가 저장되었다는 관점이 아니라, DRAM array 전체의 재사용 가능성과 다음 Access를 위한 초기 조건 확보라는 시스템적 관점에서 보셔야 이해가 되실 것 같습니다.

- 0

- 1

- 11

질문&답변

[Footprint]

안녕하세요, 답변 남겨드립니다.우선 증상으로 보아 라이브러리 테이블과 폴더 구조, 그리고 Footprint 이름 매칭 세 가지 중 하나가 어긋난 경우가 가장 유력합니다. KiCad 9.0에서는 개별 .kicad_mod 파일을 직접 참조하지 않고, 반드시 .pretty 폴더 단위로 “라이브러리 테이블”에 등록해 사용합니다. 따라서 Footprint 필드에 D:/.../SS34.kicad_mod처럼 절대경로를 적어도 동작하지 않습니다. 반대로, 라이브러리 테이블에서 부여한 닉네임과 .kicad_mod 내부의 Footprint 이름이 정확히 일치해야 Nickname:FootprintName 형식으로 인식됩니다. 예를 들어 MyDiodes.pretty 안에 있는 파일의 첫 줄이 (footprint "D_SMA" ...)라면, 회로도에서 MyDiodes:D_SMA로 써야 합니다. MyDiodes:SS34처럼 임의의 이름을 쓰면 “footprint not found”가 발생합니다.다음과 같이 재구성하시면 대부분 해결됩니다. 먼저 D:/PCB_LIB/1 아래를 부품 군별 .pretty 폴더로 정리합니다. 예시로 D:/PCB_LIB/1/Diodes_SMA.pretty에 SS34 관련 .kicad_mod, D:/PCB_LIB/1/TVS_SMB.pretty에 SMBJ5.0A 관련 .kicad_mod, D:/PCB_LIB/1/Regulators.pretty에 AMS1117 관련 .kicad_mod를 둡니다. 그런 다음 Preferences → Configure Paths에서 사용자 변수를 하나 정의합니다. 예를 들어 MY_FP_DIR = D:/PCB_LIB/1처럼 등록하면, 경로 기술을 ${MY_FP_DIR}/Diodes_SMA.pretty처럼 표준화할 수 있어 프로젝트 이동 시 경로 깨짐을 줄일 수 있습니다. 팀 협업이나 포트폴리오 공유를 고려하면, 프로젝트 루트 상대경로 ${KIPRJMOD}/lib/footprints/...를 쓰는 편이 더 안전합니다. 실제 업무에서는 Git으로 footprints/*.pretty를 버전 관리하고, 프로젝트 라이브러리 테이블에 ${KIPRJMOD} 기반 경로를 등록해 아카이브 이슈를 원천 차단합니다.이제 라이브러리 테이블을 점검합니다. PCB Editor 또는 Footprint Editor에서 Preferences → Manage Footprint Libraries를 열고, Global 또는 Project 탭에서 “Add existing library”로 .pretty 폴더를 추가합니다. Plugin Type은 “KiCad”로, Library Path는 ${MY_FP_DIR}/Diodes_SMA.pretty처럼 폴더 경로여야 합니다. 같은 닉네임이 Global과 Project에 중복되면 Project가 우선합니다. 실무에서도 종종 “Global의 정상 경로를 Project의 잘못된 경로가 가려버려서” 브라우저에 안 보이는 사례가 있습니다. 닉네임 중복이 있으면 Project 쪽을 삭제하거나 닉네임을 바꿔 충돌을 제거해 주십시오. 저장 후 Footprint Browser 좌측 패널에 방금 등록한 닉네임이 나타나야 하며, 보이지 않으면 KiCad를 재시작해 캐시를 초기화하는 방법이 가장 빠릅니다.폴더 구조와 라이브러리 테이블이 올바른데도 인식이 안 된다면 .kicad_mod 파일 자체를 확인해 보십시오. 파일을 열어 첫 줄의 Footprint 이름을 정확히 파악하시고, 그 이름으로 브라우저 검색이 되는지 확인합니다. 예를 들어 SS34 벤더에서 받은 파일 내부 이름이 "SS34_SMA"일 수 있으므로, 회로도 Footprint 필드는 MyDiodes:SS34_SMA로 입력해야 합니다. 반대로, .kicad_mod가 구버전 포맷이거나 파일 헤더가 손상된 경우가 드물게 있습니다. 이때는 Footprint Editor에서 File → Import → Footprint로 파일을 불러온 뒤, 새로운 사용자 라이브러리로 Save As하여 포맷을 최신으로 변환하면 인식률이 크게 올라갑니다.가장 안정적인 등록 방식은 프로젝트 내부에 lib/footprints 폴더를 만들고 ${KIPRJMOD}/lib/footprints/…/*.pretty로 구성한 다음, Project Library로만 등록하는 것입니다. 이렇게 하면 프로젝트를 다른 PC로 옮겨도 경로가 그대로 유지됩니다. 반면 Global Library는 여러 프로젝트에서 재사용할 표준풋프린트에 적합하지만, 닉네임 충돌이 생기면 문제 원인 파악이 늦어질 수 있습니다. 실무에서는 공용 표준은 Global, 프로젝트 특화는 Project로 분리하고, 모두 Git으로 버전 태깅해 추적 가능성을 확보합니다.포트폴리오 용도로는 KiCad 기본 Footprint를 쓰는 게 훨씬 안전합니다. SS34는 패키지 규격이 DO-214AC(SMA)이므로 Diode_SMD:D_SMA가 합리적이며, SMBJ5.0A는 DO-214AA(SMB)이므로 Diode_SMD:D_SMB가 대응됩니다. AMS1117은 탭이 Pin2인 SOT-223-3이 일반적이므로 Package_TO_SOT_SMD:SOT-223-3_TabPin2가 적합합니다. 기본 라이브러리는 IPC-7351 가이드를 기반으로 패드 사이즈, 코트야드 여유(일반적으로 0.25~0.5 mm), 솔더마스크 클리어런스(기본값 0.05 mm 수준)가 합리적으로 설정되어 있어 초반에는 이대로 쓰는 편이 오류를 줄입니다. 양산을 전제로 하면 각 벤더의 Recommended Land Pattern 수치와의 차이를 정량 비교해 검증하는 절차가 필요합니다. 예를 들어 패드 길이 산정은 L_pad = L_terminal + toe + heel처럼 계산하며, toe/heel 여유는 리플로우 공정과 부품 공차에 따라 ±0.1~0.2 mm 범위에서 조정됩니다. 실제로 SMA 다이오드에서 부품 단자 도금 길이가 1.3 mm, toe 0.2 mm, heel 0.2 mm라면 패드 길이는 약 1.7 mm로 설정하는 식으로 검토합니다. 기본 라이브러리의 패드가 벤더 권장치 대비 ±0.1~0.2 mm 범위에 들어오면 그대로 사용해도 조립성에 문제없는 경우가 많습니다.마지막으로 빠르게 진단하는 실무 팁을 정리해 드립니다. Footprint Browser 좌측에서 새 닉네임이 보이지 않으면 라이브러리 테이블 경로 또는 닉네임 충돌 문제입니다. 닉네임은 보이는데 내부 풋프린트만 안 보이면 .kicad_mod 내부 이름이 예상과 달라 매칭 실패일 가능성이 큽니다. Footprint Editor에서 New Library를 같은 폴더에 생성이 된다면 파일시스템 권한과 경로 접근성은 정상이라는 뜻이고, 이 경우 테이블 설정만 바로잡으면 해결됩니다. 반대로 Import 시 오류가 뜨면 파일 포맷 문제이므로 재저장을 통해 최신 포맷으로 변환하십시오. 경로 표기는 가급적 ${변수}/…/*.pretty 형태의 슬래시(/) 구분자를 사용하시면 Windows에서도 안정적으로 동작합니다.질문 주신 상황에서는 프로젝트 루트에 lib/footprints를 만들고 ${KIPRJMOD}/lib/footprints/Diodes_SMA.pretty와 ${KIPRJMOD}/lib/footprints/Regulators.pretty를 Project Library로만 등록한 뒤, 회로도에서 Diodes_SMA:D_SMA, Diodes_SMA:D_SMB, Regulators:SOT-223-3_TabPin2처럼 기본 풋프린트를 먼저 매칭하시길 권합니다. 이후 필요 시에만 벤더 전용 풋프린트를 추가해 대체하면, 현재의 “footprint not found” 병목을 우회하면서 레이아웃 단계로 안전하게 진입하실 수 있습니다.

- 0

- 1

- 17

질문&답변

PCB HW 설계 & 회로설계 직무면접 대비하기

안녕하세요, 답변 남겨드립니다.말씀 주신 것처럼 신입이 면접에서 “제가 개선했습니다”라고 강하게 어필하기는 쉽지 않습니다. 하지만 현업에서는 실제 보드 제작 후 반드시 발생하는 이슈들이 존재하고, 이를 설계 단계에서 어떻게 미리 고려했는지를 설명하면 충분히 강점을 드러낼 수 있습니다. 몇 가지 대표적인 사례를 들어보겠습니다.첫 번째로, Ethernet PHY EMI/ESD 이슈입니다. ESD 보호 다이오드(TVS)의 경우, IEC 61000-4-2 규격에 따라 ±8 kV (Contact), ±15 kV (Air) 방전을 견뎌야 합니다. 따라서 RJ45 근처에 배치하는 TVS 다이오드는 Clamping Voltage가 약 12 V 이하, Capacitance는 3 pF 이하인 소자를 선택해야 합니다. EMI의 경우, Class B 규격에서는 30 MHz~1 GHz 대역에서 방사 잡음이 40 dBμV/m 이하(3 m 거리 기준)로 제한됩니다. 따라서 면접에서는 “PHY 설계 시 RJ45 포트에 ±8 kV IEC 규격을 만족하는 ESD 다이오드를 배치하고, EMI 대역(30 MHz 이상)에서 리턴 패스가 끊기지 않도록 GND via를 5 mm 간격 이하로 Stitching했습니다”라고 말하면 설득력이 생깁니다.두 번째로, Motor Driver 전류 및 Power Plane 이슈입니다. 예를 들어 VM = 12 V, 최대 전류 2 A 모터를 구동한다고 가정하면, 스위칭 순간 전류 피크는 2배 이상, 즉 4~5 A까지 올라갑니다. 일반적인 1 oz(35 μm) 구리 두께에서 PCB 패턴 폭 1 mm가 약 1 A 정도를 안전하게 흘릴 수 있으므로, 45 A를 처리하려면 최소 45 mm 폭이 필요합니다. Via 전류 용량은 직경 0.3 mm, 구리 두께 1 oz일 때 약 0.3~0.5 A 수준이므로, 모터 드라이버 전원 루프에는 최소 8~10 개의 Via를 병렬 배치해야 안정적입니다. 따라서 답변 시 “Motor Driver 전원 루프에서는 최대 5 A 전류가 흐를 수 있다고 가정하고, Plane 폭을 5 mm 이상 확보하고, Via는 병렬로 8개 이상 배치하여 IR Drop과 과열 문제를 예방했습니다”라고 말씀하시면 좋습니다.세 번째로, ADC/DAC Crosstalk 문제입니다. 보통 12-bit ADC의 LSB 전압 분해능은 3.3 V 전원 기준으로 약 0.8 mV입니다. 이때 디지털 스위칭 잡음이 10 mV 수준으로 유입되면, ADC는 ±10 LSB 이상 오차가 발생하여 무의미한 값이 됩니다. 따라서 설계 시 Analog GND와 Digital GND를 분리하고, Guard Ring을 두르며, 디커플링 캐패시터(0.1 μF + 10 nF)를 ADC 핀 근처 1 mm 이내에 배치해야 합니다. 면접에서는 “ADC 입력의 노이즈를 ±1 LSB, 즉 약 1 mV 이내로 유지하기 위해 AGND와 DGND를 분리하고, Guard Ring을 형성했으며, Decoupling Capacitor를 핀 바로 옆에 배치했습니다”라고 구체적으로 말하는 것이 좋습니다.네 번째로, IR Drop과 Power Integrity입니다. 예를 들어 STM32 MCU가 동작할 때 최대 전류가 100 mA라고 하면, 3.3 V에서 50 mV 이상의 IR Drop이 생기면 정상 동작에 문제가 생길 수 있습니다. 따라서 전원 라인에서 허용 가능한 IR Drop은 보통 공급 전압의 12% 이내, 즉 3.3 V 기준 3366 mV 이하로 설계하는 것이 일반적입니다. 면접에서는 “STM32 전원망에서 IR Drop을 50 mV 이하로 제한하기 위해 전원 핀마다 0.1 μF Decoupling Capacitor를 배치하고, 전원 Plane에서 MCU까지의 Trace 폭을 0.3 mm 이상 확보했습니다”라고 말하면 구체적인 설계 기준을 제시할 수 있습니다.정리하면, 면접 대비 답변을 준비할 때는EMI/ESD → 규격 수치 (±8 kV, 30 MHz~1 GHz 대역 40 dBμV/m 이하)Motor Driver → 전류 용량 (5 A, Via 개수 8개 이상, 패턴 폭 5 mm 이상)ADC/DAC → 노이즈 허용치 (±1 LSB ≈ 1 mV)IR Drop → 전원 강하 허용치 (3.3 V의 1~2% = 33~66 mV 이하)이 네 가지를 근거로 말씀하시면 훨씬 전문적으로 보일 수 있습니다.

- 0

- 2

- 27

질문&답변

Power plane 및 via 질문

안녕하세요, 답변 남겨드립니다.말씀해주신 Power Plane 구분은 단순히 시각적으로 구분하는 것 이상의 의미가 있습니다. 실제 PCB 설계에서 Power Plane은 전류 용량과 신호 무결성을 동시에 고려해야 하기 때문에, 갈색 막대로 표시한 구분선이 있다면 이는 실질적으로 서로 다른 전원 도메인을 분리하기 위한 의도일 가능성이 큽니다. 예를 들어 STM32 MCU의 3.3V 전원과 Motor Driver의 VM (예: 12V 혹은 24V) 전원을 동일한 구리면에 섞어서 배치하면, Motor Driver의 스위칭 노이즈가 MCU 전원망으로 쉽게 유입되어 시스템 동작에 치명적인 영향을 줄 수 있습니다. 따라서 Power Plane은 반드시 실제 레이아웃 상에서도 분리해야 하고, 필요하다면 Ferrite Bead나 LDO를 통해 재결합하는 방식으로 설계해야 합니다.Via에 대해서는 기본적으로 관통홀(Through-hole via)은 모든 Layer를 관통하기 때문에 특별히 Layer를 지정하지 않아도, 상단 Layer에서 하단 Plane까지 자동으로 연결됩니다. 하지만 실제 설계에서는 “어느 Plane과 연결되는지”를 명확히 지정해야 합니다. 예를 들어, 3.3V Plane과 연결하고자 한다면, via 패드 속성을 “Net = 3V3”으로 설정해야 하고, PCB 툴에서 해당 Plane이 존재하는 Layer와 자동으로 연결됩니다. 만약 중간 Layer(예: Inner Layer 2 = GND Plane, Inner Layer 3 = 3.3V Plane)와만 연결되길 원한다면, Blind Via 혹은 Buried Via를 정의해야 하고, CAD 툴에서 Layer Pair를 지정해야 합니다.현업에서 자주 쓰는 방법은 Power Distribution Network(PDN)을 고려해 via 개수를 정량적으로 배치하는 것입니다. 예를 들어 MCU의 VDD 핀 하나에 대하여 100mA 정도 전류가 흐른다고 하면, 일반적인 0.3 mm via 하나의 허용 전류 용량이 약 300~500 mA 수준이므로, 전류적으로는 via 하나로 충분합니다. 하지만 고속 디커플링 경로나 Motor Driver의 스위칭 전원 경로에서는 전류가 순간적으로 수 A 이상 흐르기 때문에, via를 병렬로 여러 개 배치하여 전류 분산을 시켜주어야 합니다. 실제로 Motor Driver VM 전원 같은 경우는 보통 한 핀에 3~4개의 via를 병렬 배치합니다.또한 신호 리턴 경로를 위해 Power Plane과 GND Plane 사이에 via를 균형 있게 배치하는 것도 중요합니다. 특히 ADC와 DAC 같은 Mixed-signal 블록에서는 Power via와 GND via를 인접 배치하여, 전류 루프 면적을 최소화해야 노이즈가 줄어듭니다.정리하면,첫째, Power Plane은 실제 PCB에서도 반드시 구분해야 하고, 단순히 색상만이 아니라 Net 단위로 Plane 분리를 적용해야 합니다.둘째, via는 관통홀 기본 속성으로 Layer 지정이 필요 없지만, Net을 지정해야 올바른 Plane과 연결됩니다.셋째, 전류 용량과 노이즈 경로를 고려하여 via 개수를 정량적으로 배치하는 것이 필요합니다.

- 0

- 2

- 24

질문&답변

레이아웃 Value값 이상

해결되었다니 다행입니다!

- 0

- 3

- 19

질문&답변

디지털 회로 설계

안녕하세요, 답변 남겨드립니다.말씀해주신 질문은 많은 분들이 혼동하는 부분입니다. "디지털 회로 설계"와 "FPGA 개발"은 밀접하게 연관되어 있지만, 업무의 범위와 관점에서 차이가 있습니다.디지털 회로 설계는 Verilog/VHDL과 같은 하드웨어 기술 언어(HDL)를 활용해 로직을 정의하는 RTL(Register Transfer Level) 단계부터 시작합니다. 이 단계에서 하는 일은 가상의 디지털 시스템을 수학적/논리적으로 모델링하는 것입니다. 예를 들어, 32-bit ALU를 설계한다고 하면, Verilog로 add, sub, and, or 등의 연산 동작을 정의하고, 시뮬레이션을 통해 Timing Violation이나 Hazard를 잡아내는 과정이 바로 디지털 회로 설계에 속합니다. 즉, 칩이든 FPGA든 ASIC이든 공통적으로 요구되는 논리 설계 능력입니다.반면 FPGA 개발은 그 설계된 RTL을 특정 FPGA 칩(예: Xilinx Zynq, Intel Stratix)에 맞게 실제 구현하는 과정까지 포함합니다. 여기에는 몇 가지 추가적인 영역이 있습니다.첫째, Synthesis와 Place & Route 과정입니다. RTL 설계는 추상적 표현이지만, FPGA는 LUT(Look-Up Table), FF(Flip-Flop), BRAM(Block RAM) 같은 자원을 사용합니다. 따라서 합성 툴을 통해 RTL을 FPGA 자원에 매핑하고, Timing Constraint를 적용해야 합니다. 이때 100 MHz 클럭에서 동작해야 한다면, SDC 타이밍 제약을 주고 STA(Static Timing Analysis)를 수행해 Slack을 확인합니다.둘째, FPGA 개발은 주변 인터페이스와의 연결까지 책임집니다. 예를 들어, ADC 데이터를 FPGA에서 받아 DSP(FFT, Filter)를 수행하고, 결과를 ARM Core로 전달해야 한다면 AXI 버스나 DDR 메모리 인터페이스를 설계해야 합니다. 이 과정은 단순히 RTL 작성이 아니라 FPGA SoC 플랫폼 수준에서 HW+SW를 통합하는 개발에 해당합니다.셋째, 검증 및 보드 Bring-up 단계입니다. RTL 시뮬레이션을 통과했더라도 실제 FPGA 보드에서 I/O 지연, 신호 무결성, 클럭 도메인 크로싱(CDC) 같은 문제들이 발생합니다. FPGA 개발자는 Logic Analyzer, ILA(Integrated Logic Analyzer) 같은 툴을 활용해 보드 상에서 동작을 검증해야 하며, 이 또한 단순 회로 설계보다는 넓은 개념의 "FPGA 개발" 범주에 속합니다.정리하면, "디지털 회로 설계"는 논리 수준의 기능적 설계를 의미하고, "FPGA 개발"은 그 설계를 특정 FPGA 칩에서 동작시키도록 합성, 구현, 인터페이스 연결, 검증까지 포함하는 더 넓은 개념이라고 보시면 됩니다. 예를 들어 CPU 파이프라인을 Verilog로 설계하는 것은 디지털 회로 설계이고, 그 CPU를 Xilinx Zynq 보드 위에 올려서 DDR, Ethernet, PCIe와 연동되도록 개발하는 것이 FPGA 개발입니다.즉, 질문 주신 것처럼 "Verilog 작성이 RTL 설계이고, 보드에 올려서 인터페이스까지 포함해 완성하는 게 FPGA 개발"이라는 이해가 정확합니다. 실무에서는 FPGA 개발자라면 두 영역 모두에 능숙해야 하고, JD에 따라 RTL 위주의 업무인지, 인터페이스 및 시스템 통합 중심의 업무인지 구분되는 경우가 많습니다.

- 0

- 1

- 33

질문&답변

4layer stack up 구조

안녕하세요, 답변 남겨드립니다.4 Layer PCB에서 외층에 시그널, 내부층에 Plane을 두는 전형적인 구조는 실무에서 가장 널리 쓰이는 마이크로스트립(Microstrip) 방식입니다. 말씀해주신 것처럼 이론적으로는 Plane 사이에 신호를 배치하는 스트립라인(Stripline)이 외부 EMI에 더 강하고 신호 무결성이 뛰어난 것이 사실입니다. 하지만 실제 보드 설계에서는 몇 가지 현실적인 이유 때문에 마이크로스트립 구조가 기본이 됩니다.첫째는 제조 난이도와 비용입니다. 4 Layer 보드는 보통 "Signal – GND – Power – Signal" 구조를 사용합니다. 만약 Stripline 구조를 적용하려면, 적어도 6 Layer 이상에서 Signal을 내부에 배치하고 그 위아래를 GND Plane으로 감싸는 형태가 필요합니다. 즉, 최소 레이어 수가 늘어나기 때문에 보드 두께 증가, 제조 단가 상승, 제작 가능 업체의 제약이 따릅니다. 예를 들어 4 Layer 보드가 1.0 mm 두께에서 일반적으로 제조된다면, 같은 규격의 Stripline 구조를 구현하기 위해서는 6 Layer, 1.6 mm 두께 이상의 보드로 올라가야 하고, 제조 비용은 약 1.5~2배 증가하는 경우가 많습니다.둘째는 유지보수와 부품 배치 편의성입니다. 신호가 외층에 위치하는 마이크로스트립 구조는 디버깅과 프로빙이 용이합니다. 반면, Stripline 구조로 내부층에 신호를 넣으면 프로브로 신호를 찍는 것이 사실상 불가능해집니다. 예를 들어, MCU의 고속 클럭이나 ADC의 입력 신호를 검증해야 할 때, 외부에서 접근 가능한 마이크로스트립 라인은 오실로스코프 프로빙이 가능하지만, Stripline은 반드시 테스트 포인트를 사전에 설계해야만 합니다.셋째는 Mixed-signal 설계 특성입니다. STM32 같은 MCU 기반 보드에서는 디지털 신호와 아날로그 신호가 혼재하기 때문에 레이아웃에서 전원/그라운드 플레인과의 커플링이 중요합니다. 마이크로스트립 구조는 GND Plane과의 인접성으로 인해 리턴 패스(Return Path)가 비교적 명확하게 확보되며, 고속 디지털 신호에서도 충분히 신호 무결성을 유지할 수 있습니다. Stripline이 노이즈 면에서는 유리하지만, 오히려 Crosstalk이 증가할 수 있습니다. 내부층에 배선된 신호끼리 평행하게 지나가면 상호 커플링이 심해져서 오히려 더 문제를 유발할 수 있습니다.마지막으로, 보드의 목적과 동작 주파수 범위도 고려해야 합니다. 예를 들어 1 GHz 이상의 고속 SerDes, DDR4 인터페이스 같은 환경이라면 Stripline 구조의 필요성이 커집니다. 그러나 STM32 기반 Mixed-signal 보드는 보통 수십 MHz~수백 MHz 대역(예: SPI 50 MHz, ADC Sampling Clock 20 MHz 등)이 주를 이루기 때문에 마이크로스트립으로도 충분히 신호 무결성을 보장할 수 있습니다.정리하자면, Stripline은 신호 품질 측면에서 더 안정적이지만, 비용·제조·디버깅·레이아웃 자유도 측면에서 불리합니다. 따라서 4 Layer 보드에서는 마이크로스트립 구조를 기본으로 하고, 정말 고속 인터페이스나 EMI 요구사항이 까다로운 경우에만 Stripline을 채택하는 것이 현업에서의 일반적인 접근입니다.

- 0

- 1

- 15

질문&답변

Grounding Rule 적용 예시

안녕하세요, 답변 남겨드립니다.질문 주신 샤시(Chassis) 그라운드는 제품의 금속 케이스나 실드와 같은 물리적인 외피에 해당하며, 전자파(EMI) 차폐 및 외부 노이즈를 효과적으로 방출하기 위한 목적을 가지고 있습니다. 반면, 보드 내부의 Plane Ground는 디지털, 아날로그, 파워 등 회로 동작을 위한 참조 전위(Reference Ground) 역할을 수행합니다.두 가지는 원칙적으로 동일하게 취급하지 않고, 연결 방식에 따라 성능이 크게 달라집니다. 보통은 DC 성분에서는 연결되지 않거나 단일 지점에서만 접지시키고, 고주파 성분에서는 캐패시터(예: 1 nF ~ 100 nF)나 EMI 필터를 통해 샤시 그라운드로 우회 경로를 만들어줍니다. 이렇게 하면 고주파 노이즈는 샤시를 통해 외부로 방출되지만, 저주파나 DC 그라운드는 회로의 기준 전위와 간섭하지 않게 됩니다.예를 들어, Ethernet PHY 같은 고속 인터페이스는 RJ45 커넥터의 Shield 핀을 샤시 그라운드에 연결하고, 보드의 Signal Ground와는 1개의 고임피던스 저항(또는 RC 네트워크)으로만 연결합니다. 이렇게 하면 ESD나 Surge가 들어왔을 때 샤시로 빠르게 방전되며, Signal Ground를 오염시키지 않습니다. 또 다른 예시는 오디오 회로입니다. 아날로그 오디오 GND와 샤시를 직접 연결하면 험(Hum) 노이즈가 생기기 쉬우므로, 10 Ω 저항이나 페라이트 비드(Ferrite Bead)를 거쳐 단일 지점에서만 접속하여 Ground Loop를 방지합니다.정리하면, 질문 주신 표현대로 “Plane Ground에서 샤시 그라운드 쪽으로 노이즈 성분을 밖으로 빼준다”는 설명은 절반 정도 맞습니다. 다만 모든 주파수 성분이 다이렉트로 나가는 것이 아니라, 고주파 노이즈만 선택적으로 배출되도록 RC, LC, FB와 같은 네트워크를 거쳐 샤시 접지로 전달하는 방식입니다. 실제 설계 시에는 PCB Layer Stack-up에서 "Signal GND, Earthing, Chassis GND"를 별도로 구분하고, 접점은 반드시 단일 지점 원칙(Single Point Grounding)을 따르는 것이 가장 일반적인 접근입니다.

- 0

- 2

- 25

질문&답변

파워와 그라운드 면은 밀접하게 결합

안녕하세요, 답변 남겨드립니다.강의에서 언급된 “파워와 그라운드 면은 밀접하게 결합시킨다”라는 부분은 사실상 내장 디커플링 캐패시터(embedded decoupling capacitor)의 개념과 연결됩니다. 파워 플레인과 GND 플레인이 얇은 유전체를 사이에 두고 배치되면, 이 두 금속판은 캐패시터처럼 동작하게 됩니다. 즉, 플레인 자체가 수 nF ~ 수십 nF 수준의 넓은 영역 고주파용 캐패시터를 형성하게 되며, 이는 고속 신호에서 발생하는 스위칭 노이즈를 억제하는 효과를 줍니다.말씀해주신 구조를 보면, 고속 신호선은 Power-GND 플레인 사이의 유전체 층 안에서 동작합니다. 이 경우, 신호선의 리턴 커런트(return current)는 가장 가까운 GND 플레인에 흐르게 되는데, 파워 플레인과 GND 플레인이 강하게 결합되어 있으면 고주파에서 전위차가 매우 작아지고, 그 결과 전류 루프 면적(loop area)이 줄어들어 방사 노이즈와 EMI가 억제됩니다. 결국 신호선 입장에서는 주변이 저임피던스 환경으로 유지되기 때문에 안정적인 전송이 가능해집니다.여기서 디커플링 캡의 역할을 비교해보면, 일반적인 외부 디커플링 캐패시터는 로컬 전원 핀 근처에 배치하여 특정 주파수 대역에서 전압 강하를 막고 에너지를 공급하는 역할을 합니다. 반면 플레인-플레인 캐패시턴스(embedded capacitance)는 PCB 자체가 넓은 주파수 대역에서 동작하는 초고주파 디커플링 네트워크처럼 작동합니다. 즉, 신호 입장에서 보면 GND 쪽으로 로컬 캐패시터가 붙어 있는 것과 유사한 효과를 가지지만, 개별 소자가 아니라 기생적으로 형성된 대면적 캐패시턴스라는 점이 다릅니다.추가로 질문 주신 “내장 캡이 기존의 디커플링이나 커플링 캡의 기생 성분으로 동작하지 않느냐”는 부분을 설명드리면, 오히려 반대의 효과가 있습니다. 즉, 내장된 파워-그라운드 캐패시턴스는 일반 디커플링 캐패시터가 담당하기 어려운 GHz 영역의 고주파 성분까지 보완해줍니다. 예를 들어, 100nF MLCC가 주로 수 MHz ~ 수십 MHz 대역에서 효과적이라면, 플레인 캐패시턴스는 수백 MHz ~ 수 GHz까지도 유효하게 기여할 수 있습니다. 실제로 DDR4, SerDes 같은 고속 인터페이스 설계에서는 디커플링 네트워크를 LRC 모델로 등가화할 때, 이 플레인-플레인 기생 캐패시턴스를 반드시 포함하여 전원 임피던스를 해석합니다.정리하면, 플레인 결합으로 생긴 내장 캐패시턴스는 고속 신호선의 리턴 패스를 안정화시키고, 고주파 노이즈 억제를 강화하는 방향으로 작용합니다. 따라서 기존 디커플링 캡과 상호 간섭이라기보다, 주파수 보완적인 협력 관계를 형성한다고 이해하시면 정확합니다.

- 0

- 1

- 22

질문&답변

LDO schematic

안녕하세요, 답변 남겨드립니다.극성(capacitor with polarity)과 양극성(non-polar or bipolar capacitor)의 가장 큰 차이는 전압 극성에 대한 허용 여부입니다. 극성 캐패시터, 대표적으로 알루미늄 전해 콘덴서나 탄탈 캐패시터는 반드시 양극(+)과 음극(–) 방향을 맞춰서 사용해야 하며, 반대로 연결하면 내부 전해질이 파괴되거나 누설 전류가 급격히 증가하여 발열 및 폭발까지 이어질 수 있습니다. 반대로, 양극성 캐패시터는 양쪽 방향으로 전압을 걸 수 있기 때문에 교류(AC) 신호나 극성이 변하는 회로에서 주로 사용됩니다.예를 들어 LDO(Low Dropout Regulator)의 출력 안정화를 위해 많이 쓰이는 출력 커패시터를 보시면, 대부분의 LDO 데이터시트에서는 ESR(Equivalent Series Resistance) 조건과 함께 특정한 정전용량 범위를 요구합니다. 이 경우 흔히 알루미늄 전해 콘덴서를 사용하는데, 출력 전압이 DC로 일정한 극성을 갖기 때문에 극성 캐패시터를 안전하게 사용할 수 있습니다. 예를 들어 3.3V LDO 출력에 10 µF 알루미늄 전해 콘덴서를 연결한다면 극성 캐패시터가 적합합니다.반면에 오디오 신호 경로나 AC 커플링 회로에서는 입력 신호가 +V와 -V로 교대로 변하기 때문에 극성 캐패시터는 사용할 수 없습니다. 이런 경우에는 필연적으로 양극성 캐패시터(보통은 필름 콘덴서, 세라믹 콘덴서, 혹은 bipolar electrolytic capacitor)를 사용합니다. 예를 들어 오디오 앰프 입력단의 커플링 콘덴서는 ±1 V의 오디오 신호가 인가되므로 극성 캐패시터 대신 양극성 캐패시터를 배치합니다.정리하자면, DC 전원 안정화(예: LDO 출력)처럼 극성이 고정된 경우에는 극성 캐패시터가 일반적이고, AC 신호 커플링이나 극성이 변하는 환경에서는 반드시 양극성 캐패시터가 필요합니다. 현업에서는 보드 설계 시 디커플링 커패시터(0.1 µF, 1 µF 등)는 대부분 세라믹(양극성)을 쓰고, 벌크 캐패시터(10 µF~100 µF)는 전해(극성)를 배치하는 식으로 혼용하는 사례가 많습니다.

- 0

- 1

- 27