お知らせ

14 件

こんにちは。

しばらく前に停止しました

電子文書(pdfファイル)ダウンロードが再び可能になりました。

インフラで講義を購入された方

資料室から電子文書をダウンロードして活用してください。ありがとう〜!

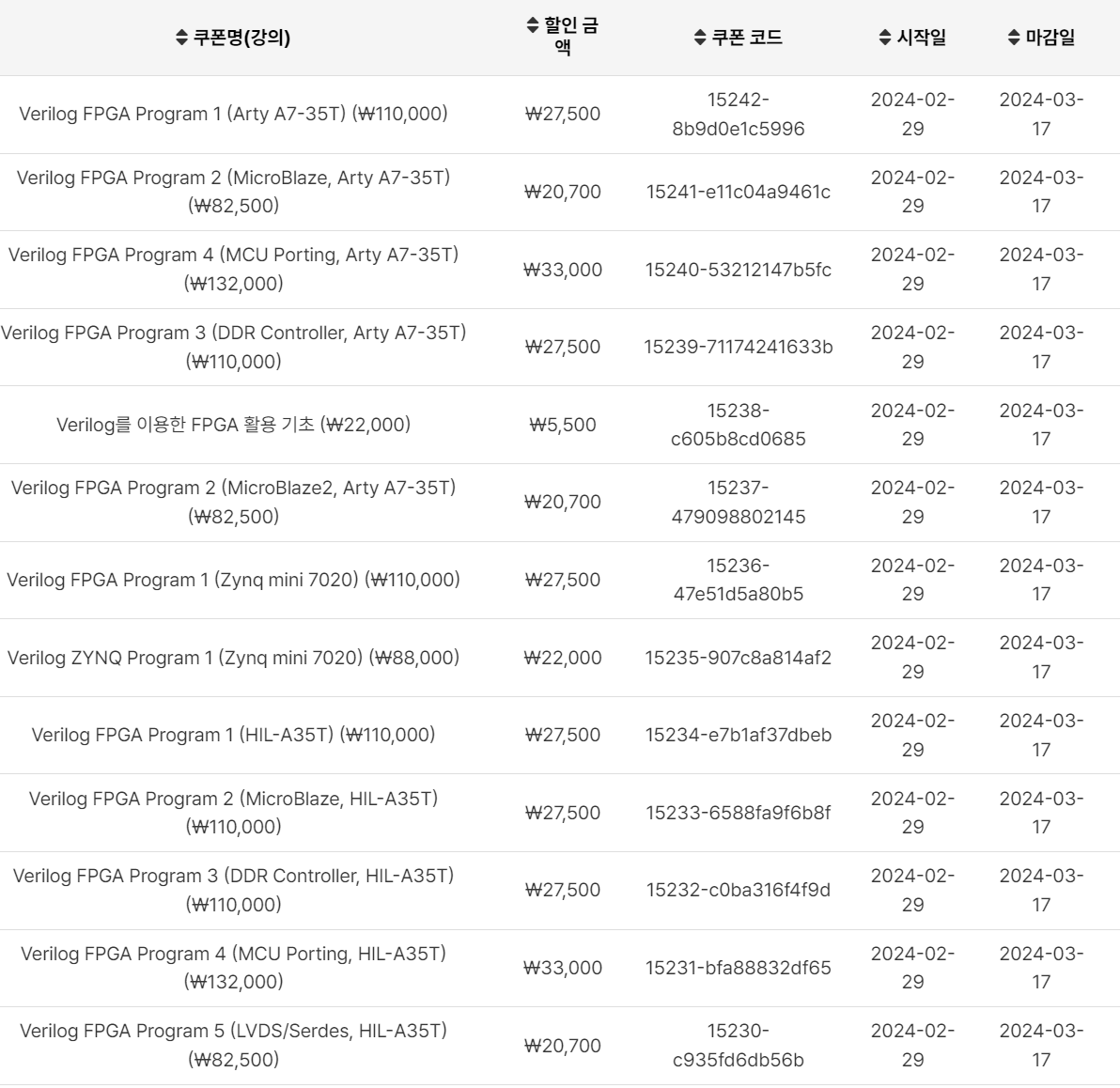

新学期を迎え、講義個別購入割引イベントを進めます。

Verilog、FPGAを学びたい方に良い機会になってください1. Verilog、FPGA関連講義割引イベント

♣講義の25%割引

♣期間:2024.02.29〜2024.03.17

♣下記の割引クーポンを利用してインプランで購入2 . HIL-A35開発ボード割引イベント

♣開発ボード15%割引

♣期間:2024.02.29〜2024.03.17

♣スマートストア: https: //smartstore.naver.com/ihilありがとう〜!

こんにちは。

開発ボードの販売を開始します。

以下のネイバースマートストアで購入できます。

スマートストアリンク: https: //smartstore.naver.com/ihil 開発ボード関連資料は以下のリンクからダウンロードできます。

開発ボード関連資料は以下のリンクからダウンロードできます。

マニュアルとテストプログラム(led、ボタン動作)があります。

ダウンロードリンク: http: //naver.me/xJqtlt1T 開発ボードはインフラストラクチャ講義用に独自開発した製品です。

開発ボードはインフラストラクチャ講義用に独自開発した製品です。Verilog FPGA Program 1(HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Controller, HIL-A35T)

Verilog FPGA Program 4 (MCU Proting, HIL-A35T )

開発ボードと講義を通じて多くのお役に立てば幸いです。

ありがとうございます〜!講義が更新されました。

講義名:FPGA MicroBlazeの実装

更新内容:第4章、第5章内容新しく更新されました。

講義を購入された方は資料室からダウンロードしてください。

今後の「FPGA MicroBlazeの実装」のレッスンは、引き続き全体の内容が更新される予定です。

ありがとうございます〜!

講義が更新されました。

Verilogを使用したFPGAの活用(v2.1)

NRZL Decoder実装内容(ch11)が追加されました。

FIFOの実装、使用に関する重要な内容です。

実務に大いに役立つと期待しています。

Verilogを使用したFPGAの活用 for Zynq (v1.2)

NRZL Decoder実装内容(ch14)が追加されました。

FIFOの実装、使用に関する重要な内容です。

実務に大いに役立つと期待しています。

講義を購入された方は資料室から無料でダウンロードしていただけます。

講義を通してたくさん助けてください。ありがとうございます。

こんにちは。

【Verilogを利用したFPGA活用 for Zynq】講義がオープンしました。

本講義は「Verilogを利用したFPGA活用」の内容をZynq mini 7020(7010)ボードに合わせて

新しく構成しました。前半

vivado 2021.1のインストール

Zynqボードに実装されたコードのダウンロードと結果の確認

後半

カウンターによるLED制御

SPI Controller

UART Controller

I2Cコントローラ

Xilinx IP

講義オープン記念で30%割引を行っています。

多くの関心をお願いします。ありがとうございます。

Verilog、FPGA講義が完了しました。

最初にはこれほどまでするとは思わなかったが、

多くの人が助けてくれて応援してくれて

ここまで来られたようです。

私の講義に関心を持ってくれた皆さんに心から感謝します。講義活用ヒントについて簡単に説明いたします。

1.講義を聞く前に、Verilogの基本的な文法をよく理解してください。

講義では文法については説明しません。基本的な文法を知っていると考えて講義が行われます。文法は基本的なものだけを知っておく必要があります (reg, wire, always, module, など)2.最初のスタートは「Verilogを使ったFPGAの活用」から始めてください。

この講義には多くの内容が含まれています。

2~3回程度精読しながら直接コードで実装し、シミュレーションで検証し、ボードに載せて確認してみてください。

verilog、fpgaを学ぶために目で学ぶことは役に立ちません。

私は総開発経歴が25年に、verilog、fpga分野では20年ほどになりました。

今でもi2c contollerを実装するには、数十回以上コーディングしてシミュレーションを検証し、これらのプロセスを経ます。

講義の紹介: https: //cafe.naver.com/worshippt/2663. 「Verilogを利用したFPGA活用基礎」編は付録として活用してください。

一度は知っておくべき内容で構成されました。

このレッスンは、今後の内容を追加して更新する予定です。

講義の紹介: https: //cafe.naver.com/worshippt/2654. FPGA MCU移植講義は開発者のスキルを一段階アップグレードできる内容です。

私は多くのプロジェクトにこの講義の内容を適用しました。

ロジックをデバッグするためにも使用され、別のMCUを外部で使用する必要がない非常に便利なソリューションです。

さらに、自由にfpga内部のメモリを活用できます。

講義の紹介: https: //cafe.naver.com/worshippt/2685. MicroBlaze講義は、2編の講義内容を正しく理解すれば、ほぼすべての内容を知ってプロジェクトに適用できます。

MicroBlazeはMCU移植に比べてパフォーマンスが非常に優れています。

一方、メモリの構成と適用にはいくつかの制約があります。

MCUポーティング、MicroBlazeの2つをすべて知っていれば、プロジェクトに応じて選択して使用できます。

軽く使用したいときはMCUポッティングを使用し、性能の良いものが必要な場合はMicroBlazeを使用すればよい。

講義紹介-1: https://cafe.naver.com/worshippt/269

講義紹介-2: https: //cafe.naver.com/worshippt/2706. DDR Controller 講義は、Image Data を処理する分野に必要な講義です。

Image Dataを処理するにはFrame Bufferが必要で、Frame BufferはほとんどDDR Memoryを使用します。

このレッスンは、DDR Controllerの作成からFramer Bufferの実装まで説明されています。

講義の紹介: https: //cafe.naver.com/worshippt/267今後はより良い内容でお探しいただけるようにします。

私の講義に関心を持ってくださった方々にもよろしくお願いします。ありがとうございます。

MicroBlaze講義がアップデート(v1.5)されました。

10-11章が新たに追加されました。

第10章では、Block Designがデフォルトで提供するBlock Memory Interfaceを実装しています。

第11章では、ユーザーロジックにBlock Memoryを追加してBlock Memory Interfaceを実装します。これを利用してUser Logic Register Mapを実装し、pwmのfrequecny、dutyを制御する例を実装します。

購入した方は資料室からダウンロードしてください。

ありがとうございます。