Hamming Code 질문

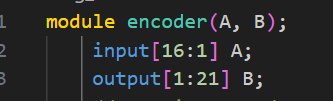

encoder의 경우, output이 [1:21]로 서술되어 있습니다.

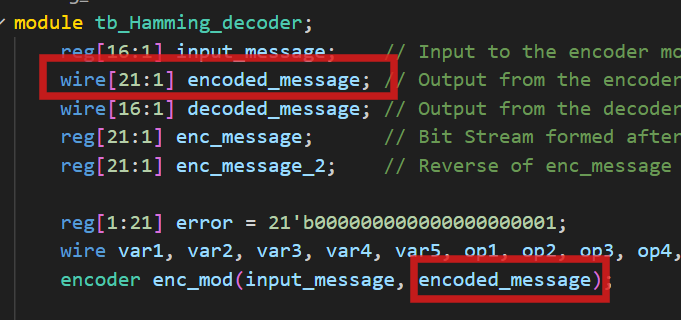

근데 tb를 보면 output인 encoded_message가 [21:1] 로 선언되었는데, 이렇게 선언하게 되면 encoded_message 에 들어오는 값은 B[21:1] 로 매칭되서 들어오게 되는건가요? 아니면 tb 코드에서 [21:1]로 잘못 선언한 것인지 궁금합니다! 감사합니다.

回答 1

0

안녕하세요, 답변 남겨드립니다.

이 부분은 제가 순서를 반대로 하긴 했네요ㅠ encoder 모듈의 output이 [1:21]로 선언되어 있다면, testbench에서도 동일하게 [1:21]로 선언하여 사용해야 합니다. 만약 testbench에서 [21:1]로 선언한다면, 비트 폭은 같더라도 인덱스 방향이 반대이므로 MSB와 LSB가 뒤집혀 매칭되게 됩니다. 이 경우 의도한 데이터와는 다르게 출력이 연결되어 시뮬레이션 결과가 올바르지 않게 나올 수 있습니다.

실무적으로는 이런 혼동을 피하기 위해 대부분 [N-1:0] 형태로 선언합니다. 예를 들어 21비트라면 [20:0]로 선언하는 것이 일반적입니다. 이렇게 하면 항상 0번 비트가 LSB, N-1번 비트가 MSB라는 암묵적인 약속이 적용되므로 협업 시에도 혼동을 줄일 수 있습니다.

따라서 이번 경우에는 testbench에서 [21:1]로 잘못 선언한 것이 맞고, encoder와 동일하게 [1:21]로 수정해야 합니다. 이후 설계 전체를 일관되게 작성하시는 것이 바람직합니다.

강의 만료일 연장 신청

0

28

2

강의자료 pdf파일

0

87

2

수강기간변경

0

73

2

프로그램 종류

0

87

1

안녕하세요 강의 도중 궁금한 점 있어서 질문드립니다!

0

83

1

수강기간 변경관련

0

62

2

수강기간 만료

0

69

2

수강 연장 문의

0

69

2

I2C SCL_Synched, SDA_Synched 질문

0

81

1

no data path질문

0

101

3

SRAM 강의 modelsim 시뮬레이션에서 inner 메모리를 Objects 리스트에서 찾으려고 하는데 안보입니다.

0

86

2

DataMem 스펙 질문

0

52

1

W_CRC 값 질문하기

0

59

1

Precharge에 대한 질문

0

163

1

tpsram spec 질문

0

62

2

학습 관련 질문 있습니다!

0

85

2

[과제7] AXI 통신 프로토콜 설계하기 문의드립니다

0

92

2

SRAM 강의 TB 작성 후 waveform 확인시에 dout이 모두 don't care 처리 관련 질문드립니다.

0

104

5

SRAM Interface Behavior(Diagram) 질문

0

133

3

vivado와 quartus 프로그램의 systhesis 결과 차이에 대해 궁금한 점 있습니다

0

182

2

tool 질문

0

91

2

CDC 메타스태빌리티 질문

0

64

1

SRAM module RTL viewer 이상

0

95

2

slave와 master 시뮬레이션

0

65

2