Inflearn コミュニティ Q&A

21강의 DUT 질문 있습니다.

作成

·

32

1

21장 코드의 case문을 보면 c_state를 아래 정의한 case들과 비교해 각각의 명령을 실행하는 것인데 여기서 S_DONE일 경우 n_state를 S_IDLE로 바꿉니다. 근데 왜 wave form에서는 바로 바뀌지 않고, 1cycle 정도 후에 바뀌나요?

또 여기서 1cycle은 어떤 것을 의미하나요?

감사합니다.

always (c_state or i_run or is_done) begin

n_state = S_IDLE;

case (c_state)

S_IDLE : if (i_run == 1)

n_state = S_RUN;

S_RUN : if (is_done == 1)

n_state = S_DONE;

S_DONE : n_state = S_IDLE;

endcase

endverilog-hdlfpga임베디드

回答 1

0

semisgdh

インストラクター

안녕하세요 🙂

그림에서 보시면,

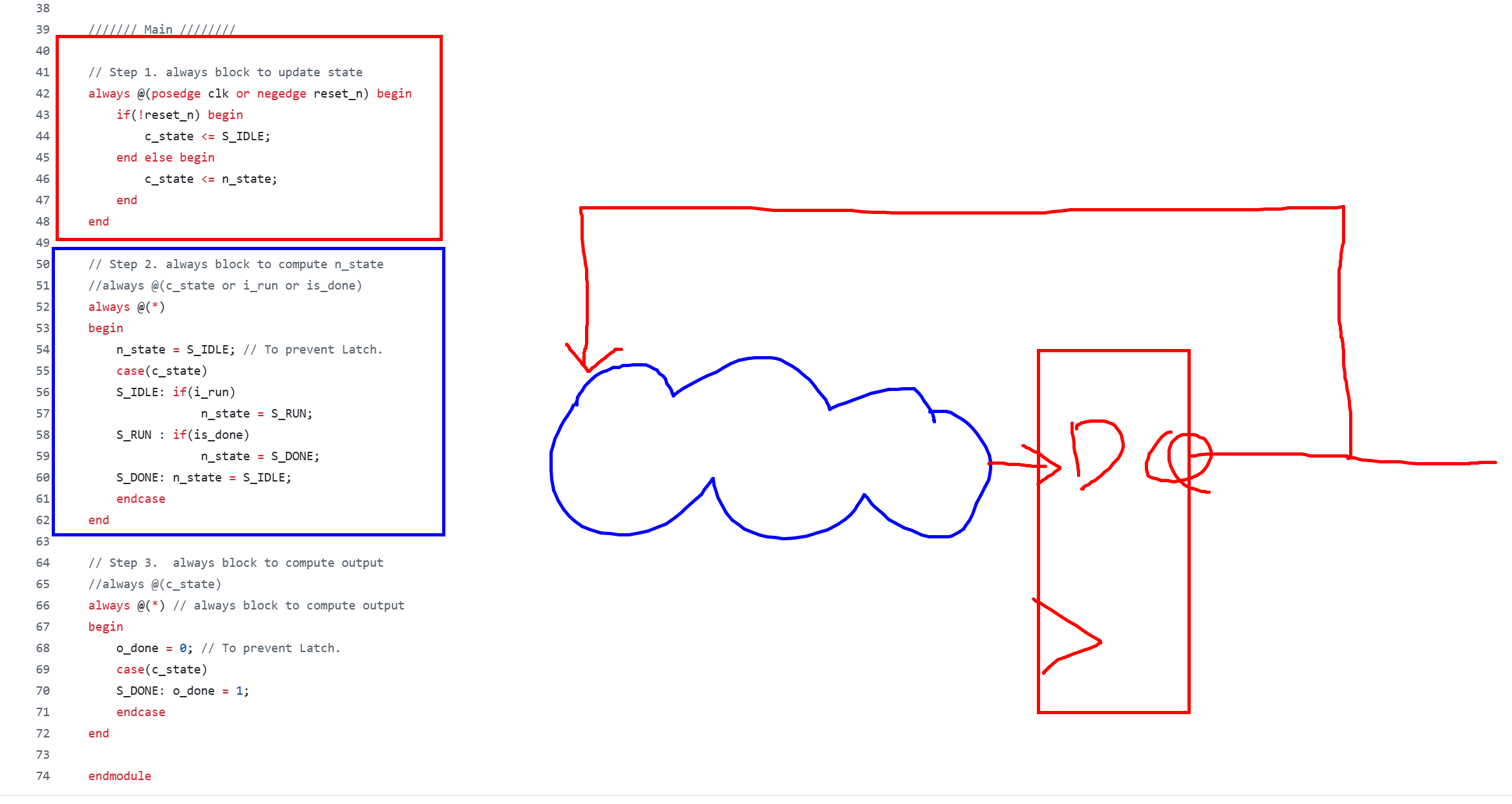

캡쳐해주신 코드는 Combinational Logic 파트입니다. (파란색 부분)

코드에서 1 cycle 변경 부분은, 다음 그림에서 빨간색 부분이 되겠습니다.

빨간색 박스 내의 코드를 보시면, clk edge 에 맞추서, c_state <= n_state 로 반영합니다.

이것이 1 cycle delay 를 만들어 냅니다.

따라서 "S_DONE일 경우 n_state를 S_IDLE 로 바꾸는데요" 이 반영된 내용은 1 cycle 뒤에 c_state 로 반영됩니다. 따라서 질문주신

"wave form에서는 바로 바뀌지 않고, 1cycle 정도 후에 바뀌나요?"

이것은 코드에서 의도한 동작입니다.

즐공하세요 🙂