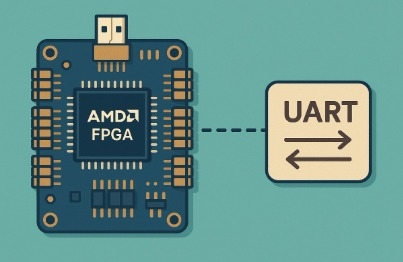

Implementing UART on FPGA

UART is the most basic and widely utilized serial communication method, making it a very suitable learning topic for beginners new to FPGA design. In this course, we will thoroughly understand the communication principles and frame structure of UART, and based on this, we will proceed with directly implementing transmit/receive logic through RTL (Register Transfer Level) design. By implementing UART on an FPGA, you can systematically develop your digital circuit design skills and gain experience verifying its operation at the actual hardware level through simulation and verification. Furthermore, by learning the method utilizing the MicroBlaze soft processor and Xilinx UART IP, you will gain a broad understanding of processor-based system design flow and interface configuration. This will enable you to acquire comprehensive development capabilities encompassing both logic design and processor design.

36 learners

Level Basic

Course period Unlimited

- Resolved

Zybo 환경에서 PL RTL UART 보드 검증 방법

안녕하세요, 강의 수강 중 문의드립니다. * 저는 아직 이해가 부족한 부분이 많아 질문 내용을 AI의 도움을 받아 정리하였습니다.<p

fpgasystem-veriloguartvivadomini9136

・

14 days ago

0

31

2

- Unresolved

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다.

7강에서 실습하려면 FPGA 보드가 필요한지 궁금합니다. 아님 맨처음에 설정에서 보드 설정이 있는데 그걸로도 가능한지 궁금합니다.

fpgasystem-veriloguartvivadolemmon78198028

・

2 months ago

0

62

1

- Resolved

5장 강의 노트 확인 부탁드립니다.

5. UART TX/RX 모듈 RTL 설계 및 시뮬레이션강좌의 강의 자료를 다운 받으면 ep06_Intergration 자료 입니다.확인 부탁드립니다.</

fpgasystem-veriloguartvivadoinair3292

・

7 months ago

0

68

2

- Resolved

RTL

RTL이 Veliog인거같은데 vhdl 버전은 없나요 ?

fpgasystem-veriloguartvivadoflak397306

・

8 months ago

0

98

1

- Resolved

멀티바이트프레임 로직 예시

FIFO를 이용하여 멀티바이트프레임 로직 구문을 작성 및 처리하는 참조 할 만한 로직 예시 가 있을까요

fpgasystem-veriloguartvivadojookd787339

・

8 months ago

0

90

2