Inflearn Community Q&A

코드 질문입니다 [AI HW Lab2]

Written on

·

502

1

안녕하세요 맛비님.

안녕하세요 맛비님.

별 다른 질문은 아니고, 예전부터 궁금했던 것인데

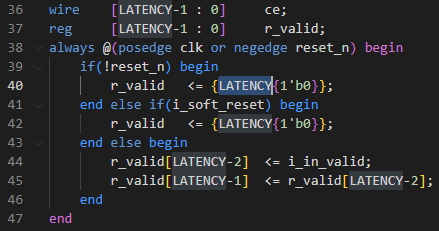

위 사진에서 40번째줄에 r_valid <= {LATENCY{1'b0}};

부분을 왜 저렇게 표현했는지 궁금합니다.

r_valid <= 0; 이렇게 해도 LATENCY가 달라짐에 따라 0의 값이 고정이지 않나요??

위에서 localparam LATENCY = 2 라고 해서 40번째 줄은 r_valid <= {2{1'b0}}; 와 같습니다.

( 2{1'b0} = 2*1'b0 = 2'b0 인건가요? )

임베디드임베디드verilog-hdlfpgacnn

Answer 1

1

semisgdh

Instructor

r_valid <= 0; 이렇게 해도 LATENCY가 달라짐에 따라 0의 값이 고정이지 않나요??

네 function 으로는 문제 없어요. 명확하게 해주고 싶어서 사용했습니다.

0 을 그대로 사용하면 32b 입니다 (기본 default)

( 2{1'b0} = 2*1'b0 = 2'b0 인건가요? )

2'b0 맞습니다.

즐공하세요 :)