Inflearn Community Q&A

zybo 보드에서 파형문제

Written on

·

307

1

안녕하세요.

zybo보드 구매해서 강의보면서 따라하고 공부중 입니다.

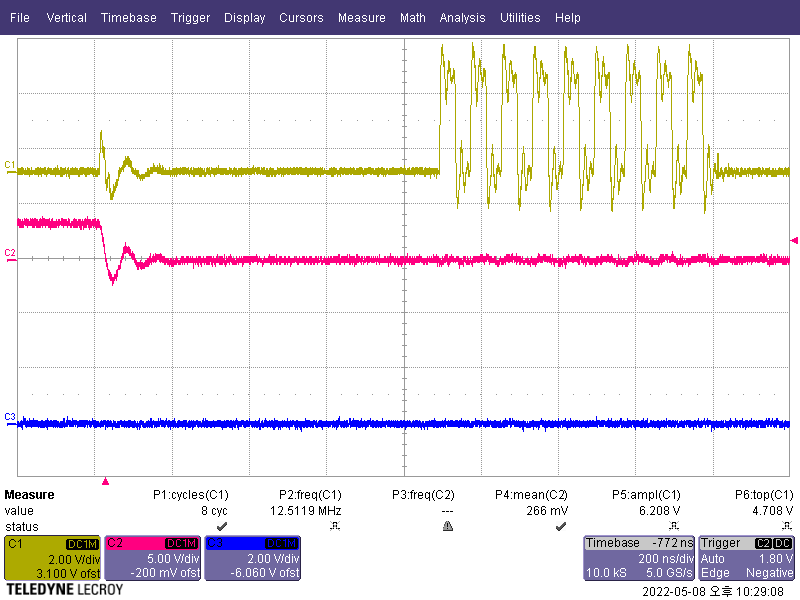

테스트중 스코프로 파형을 찍어 봤는데요

그림처럼 스위칭 노이즈로 보이는 노이즈가 상당히 크게 발생됩니다.

이런 노이즈등은 FPGA 설계의 문제 아니면 다른 원인이 있는건지 또는 좀더 안정시킬 수 있는 방법이 있는지 궁금합니다.

직접적인 강의의 코드질문이 아니라서 죄송합니다만

강의 내용중에 하드웨어 직접 다운로드하고 이를 검증하는 부분들이 빠져 있는것 같아서 조금 아쉽네요. ^ ^;

미리 감사드립니다.

Answer 1

0

안녕하세요 :)

먼저 강의 내용 외의 질문은 정중히 양해 부탁드릴께요.

테스트중 스코프로 파형을 찍어 봤는데요

그림처럼 스위칭 노이즈로 보이는 노이즈가 상당히 크게 발생됩니다.

이런 노이즈등은 FPGA 설계의 문제 아니면 다른 원인이 있는건지 또는 좀더 안정시킬 수 있는 방법이 있는지 궁금합니다.

FPGA Pin 부분을 찍으신 것 같은데, 이미 이렇게 출력이 되는 것을 Verilog HDL code 로 수정하기는 어려워 보입니다. PCB 회로 레벨로 가셔야 해요. (여기는 비메모리 설계를 배우는 강의입니다.) Noise 흡수를 위해 Cap 을 board 에 다신다던가 하는?

스코프의 파형이 버튼 스위치라면, debouncer 설계를 하시면 될 것 같아요. (근데 아닌 것 같아요.. 혹시모르니 링크남겨요.)

https://chipmunklogic.com/digital-logic-design/debouncing-switches-in-verilog-vhdl/

강의 내용중에 하드웨어 직접 다운로드하고 이를 검증하는 부분들이 빠져 있는것 같아서 조금 아쉽네요. ^ ^;

저도 모든 걸 다루지 못해서 이 부분은 아쉽습니다. ㅠ.ㅠ

Season2 에 반영할 수 있으면 다뤄보겠습니다.

즐공하세요 :)