Inflearn Community Q&A

Counter 설계 관련 질문3

Resolved

Written on

·

535

1

1. 뭐랑 뭐가 다른것인가?에 대한 재질문

reg [6:0] cnt_always; 가 합성될 때는 1bit register 7개가 쌓여서 회로가 합성됩니다.

reg cnt_always [6:0]; 문법을 사용하면1bit register 7개를 선언한 문법입니다

그렇다면 회로가 합성이 될 때 reg [6:0] cnt_always; 와 reg cnt_always [6:0];가 동일한 방식으로 합성되는 것인가요?

두 문법 다 회로로 합성될 때는 결과적으로는 1bit register 7개가 생기는 것 아닌가요?

2. 전 질문에서 3번째에 해당하는 내용입니다. 제가 굉장히 이상하다고 느꼈던 점은

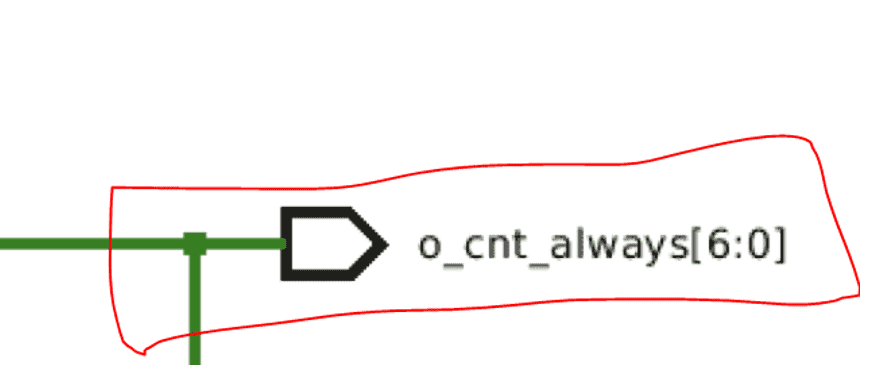

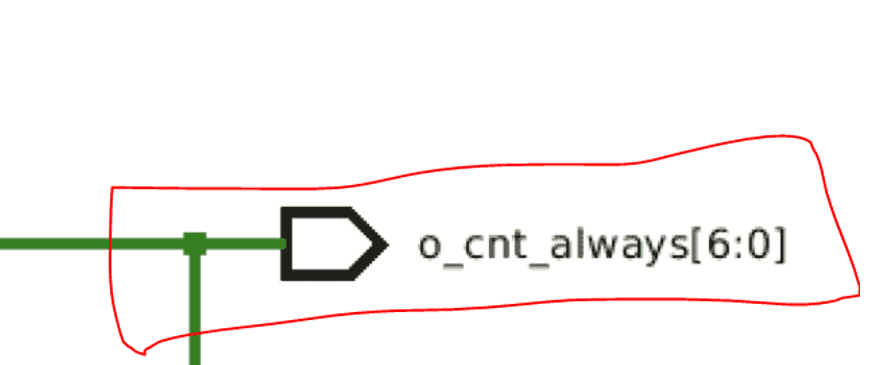

output [6:0] o_cnt_always를 회로로 합성하면 아래 사진과 같이 표현됩니다

그렇다면 output reg o_cnt_always; 를 회로로 합성하면 어떻게 되는것인가가 이상하다고 느꼈습니다

보내주신 링크에도 "The module ports model the pins of hardware compoents"라는 문장이 있습니다.

모듈의 포트는 하드웨어에서 핀을 의미한다라는 뜻인데...제 생각에는 레지스터도 아니고 단순히 전기신호가 드나드는 핀이 정보를 저장한다?! 이게 이상하게 느껴집니다. 출력포트의 자료형이 reg형이라면 회로로 어떻게 합성된다는 뜻인가요?

===> Out Port 에 reg 를 사용하나, 별도로 reg 를 사용하나, 합성 결과는 동일합니다. (회로적으로 동일하기 때문에, 어느 문법이 불이익을 받아야 할 이유가 없다 생각합니다.)

라고 맛비님이 답해주셨는데 그렇다면 output reg [6:0] o_cnt_always에서도 출력 포트는 위의 사진과 같이 합성되고

reg 부분은 따로 합성되는 것인가요?

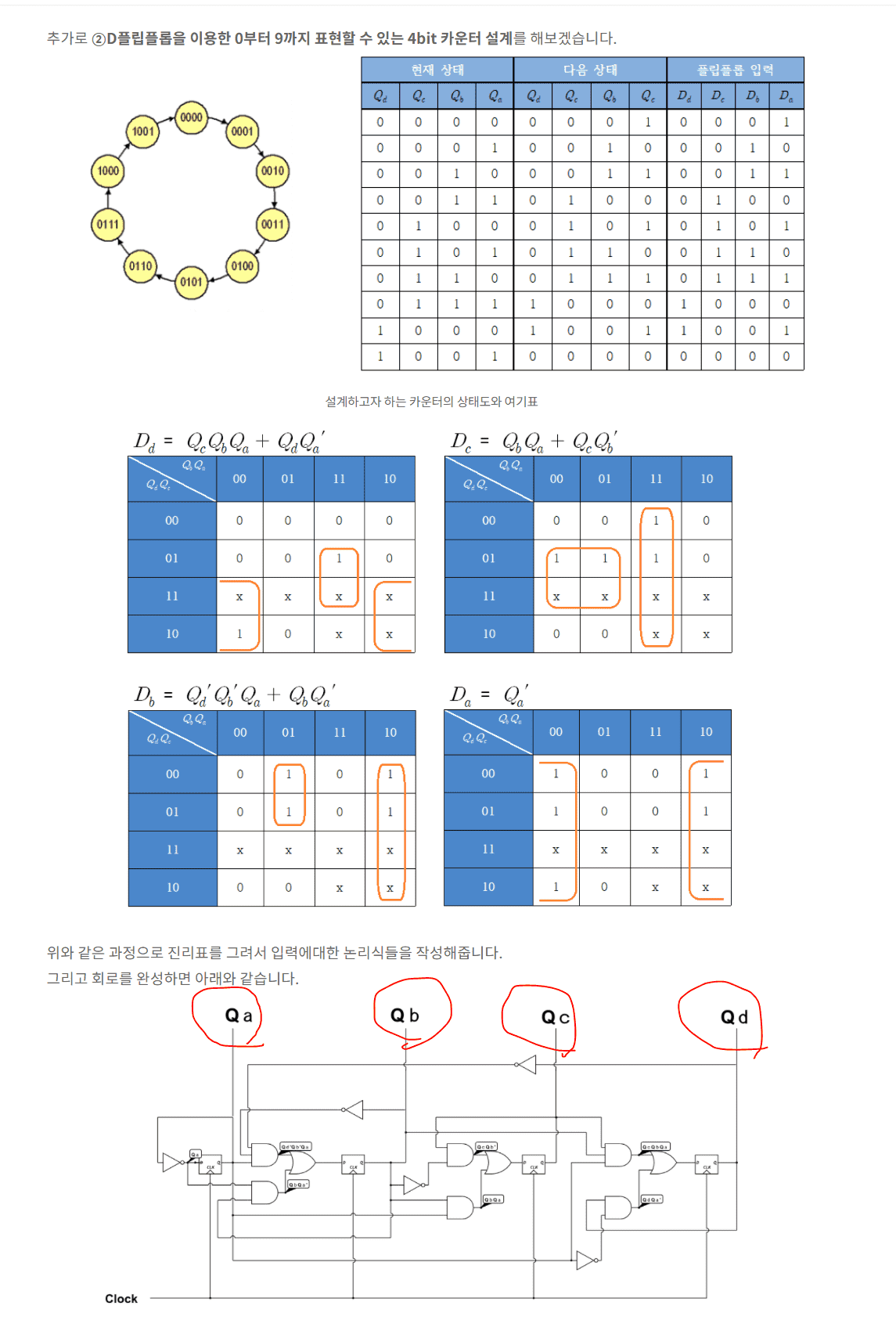

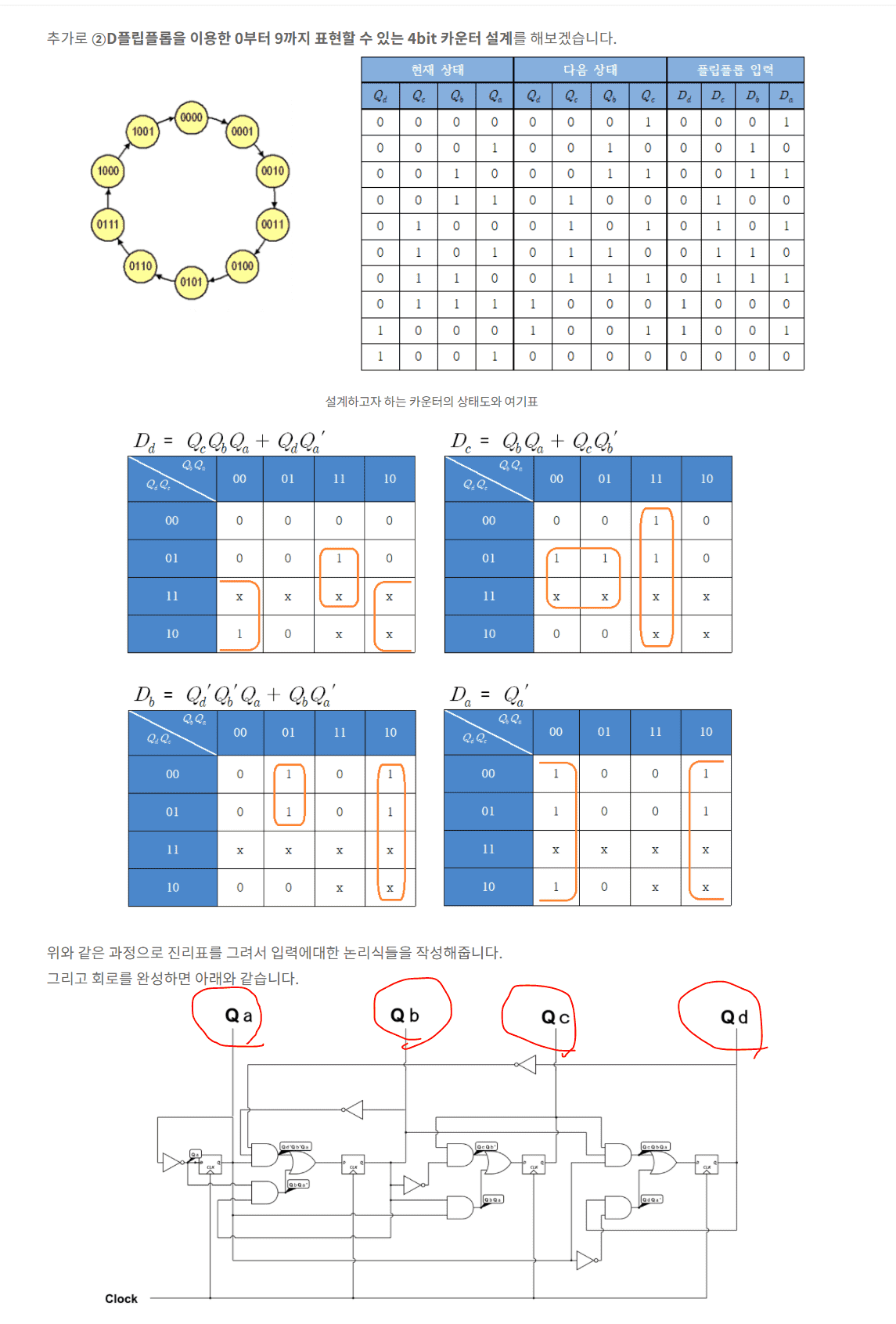

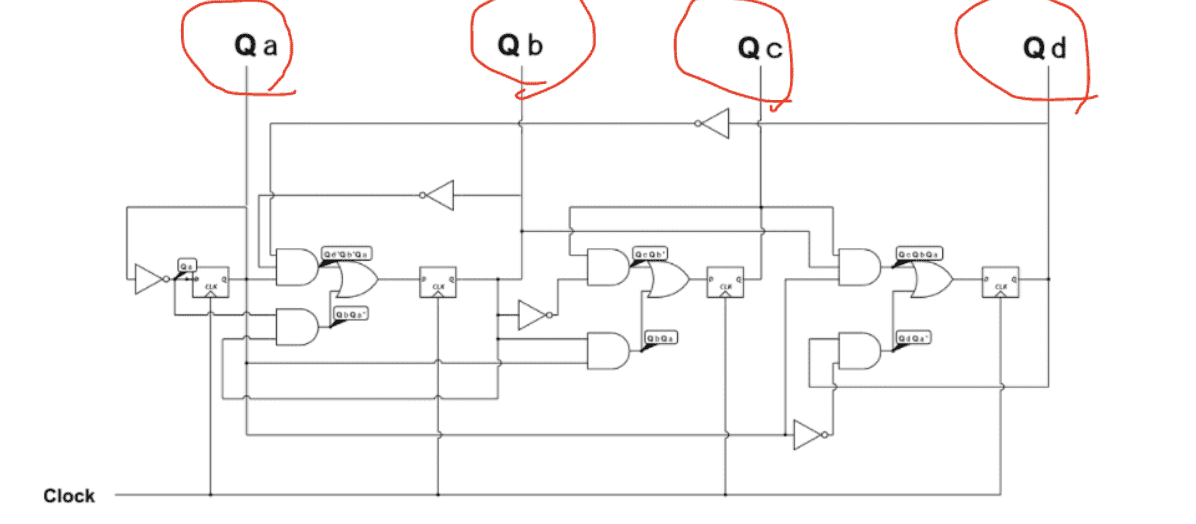

3. 제가 생각한 카운터를 다시 인터넷에서 찾았습니다.

QaQbQcQd = 0001 QaQbQcQd = 0010 QaQbQcQd = 0011 이렇게 하면 카운터 기능을 하는 것 아닌가요?

이런 방식의 카운터와 맛비님께서 보여주신 카운터의 차이가 무엇인지 궁금하다는 뜻이었습니다. 맛비님께서는 추상화의 차이다 라고 말씀해주셨는데. 추상화에서만 차이가 있고 나머지 부분은 동일한 것인가요?

Answer 1

1

질문이 구체화가 되가는군요!

1. 뭐랑 뭐가 다른것인가?에 대한 재질문

reg [6:0] cnt_always; 가 합성될 때는 1bit register 7개가 쌓여서 회로가 합성됩니다.

reg cnt_always [6:0]; 문법을 사용하면1bit register 7개를 선언한 문법입니다

그렇다면 회로가 합성이 될 때 reg [6:0] cnt_always; 와 reg cnt_always [6:0];가 동일한 방식으로 합성되는 것인가요?

이거는 "vector" 와 "array" 의 문법 기술 차이인데요. 저는 합성 결과가 동일하다 생각하는데, 합성 Tool 마다 차이가 있을 수 있을 것 같아요. (간혹 array를 이상하게 인식하는 Tool 들이 있어요.. 그 케이스만 제외한다면 "동일하다" 답변드리고 싶습니다. )

두 문법 다 회로로 합성될 때는 결과적으로는 1bit register 7개가 생기는 것 아닌가요?

네, 맞아요.

2. 전 질문에서 3번째에 해당하는 내용입니다. 제가 굉장히 이상하다고 느꼈던 점은

output o_cnt_always를 회로로 합성하면 아래 사진과 같이 표현됩니다

그렇다면 output reg o_cnt_always; 를 회로로 합성하면 어떻게 되는것인가가 이상하다고 느꼈습니다

보내주신 링크에도 "The module ports model the pins of hardware compoents"라는 문장이 있습니다.

모듈의 포트는 하드웨어에서 핀을 의미한다라는 뜻인데...제 생각에는 레지스터도 아니고 단순히 전기신호가 드나드는 핀이 정보를 저장한다?! 이게 이상하게 느껴집니다. 출력포트의 자료형이 reg형이라면 회로로 어떻게 합성된다는 뜻인가요?

port != reg

"2 line 을 1 line 으로 적은 문법일 뿐입니다."

혹시 두개의 코드가, 결과가 다르게 나오나요? 이거는 Test 해봐주시겠어요? (해보면 바로 답이 나오니까, 합성까지 해서 Util resource 사용량 까지 알려주시면 더 좋구요. 저는 동일할꺼다 예상합니다.)

case 1. output reg o_cnt_always;

case 2. output o_cnt_always; reg o_cnt_always;

3. 제가 생각한 카운터를 다시 인터넷에서 찾았습니다.

QaQbQcQd = 0001 QaQbQcQd = 0010 QaQbQcQd = 0011 이렇게 하면 카운터 기능을 하는 것 아닌가요?

아.... 이거 였구나... 이제!!! 이해했습니다. 뭔가 했네요.

Counter 기능을 해요.

이런 방식의 카운터와 맛비님께서 보여주신 카운터의 차이가 무엇인지 궁금하다는 뜻이었습니다. 맛비님께서는 추상화의 차이다 라고 말씀해주셨는데. 추상화에서만 차이가 있고 나머지 부분은 동일한 것인가요?

"추상화 차이" + 사람이 Optimize 를 하느냐, Tool 이 Optimize 를 하느냐 도 추가가 되어야 설명이 될 것 같아요. 그림으로 올려주신건 사람이 Optimize 하였고, 해당회로를

Verilog HDL 을 Gate Level 로 기술해야 합니다.

저는 Behavior 로 기술하였고, Tool 에 Optimize 를 맡겼어요.

그럼 두개가 결과가 같으냐?!!!! 정답은 해봐야 안다.

하지만 저의 감으로는 다를 것이다. 왜냐하면, FPGA 는 Resource 를 사용하는 것이기 때문에, 저렇게 올려주신 Gate 회로처럼 Gate Level 로 resoucre 를 사용하지 않을 것이다. 정말 다를지 궁금하다면 해보시고 공유 부탁드려요.

점점 이해가 됩니다 :)

저도 완벽하게 알지는 못해서, 먼저 양해의 말씀을 드립니다. (해봐야 안다라는 문장을 몇번을 쓴건지.. ㅠㅠ)

저도 YM님 덕분에 많이 배웠습니다.

근래 설계하면서 이렇게 deep 하게 생각해본 적이 없었어요. (눈 앞의 설계에만 급급한 나머지)

당연히 교수님보다는 제가 부족하겠지만, 질문 올려주시면 제가 아는 범위내에서는 꼭 답변 드리겠습니다.

즐공하세요 :)

학교에서 verilog 수업을 들을 때는 말로만 수업이 진행되어서 답답한 점이 많았습니다

저 문법적 표현이 그래서 어떻게 회로로 표현되는거지? 어떻게 생겼다는거지?? 내가 이런 회로를 그리고 싶은데 이건 어떻게 문법적으로 표현하지? 라는 궁금점이 많았지만

끝내 해결을 하지 못했었습니다

제가 잘 모르다보니 질문이 난잡한데, 그럼에도 불구하고 끝까지 답변 주셔서 정말 감사합니다

오늘 RTL analysis라는 좋은 기능도 배워가고, 카운터 공부하면서 verilog로 기술한 회로가

어떻게 합성되는지 조금은 알 것 같습니다. 답변 감사합니다