14장 Cycle 관련, Testbench 코드.

63

12 asked

안녕하세요 🙂

[1. 질문 챕터] : eg) 몇 장, 몇 분 몇 초 쯤. or 수강생 분들이 봤을 때 어디구나?! 할 수 있게 표기 부탁 드려요.

14장에 tb에 negedge clk 오류?

[2. 질문 내용] : eg) 질문 내용을 자유롭게 작성해주시면 되겠습니다 🙂

14장에 53번째 negedge clk 오류? 로 인한 주석 처리 질문을 찾고 input과 ouput의 latency 3cycle로 동작을 확인하였습니다.

여기서, i_vaild와 o_vaild는 시작은 3cycle인데 마지막은 2.5cycle로 동작하는 거 같은데, 3cycle이 의도 된 동작이 맞는거죠?

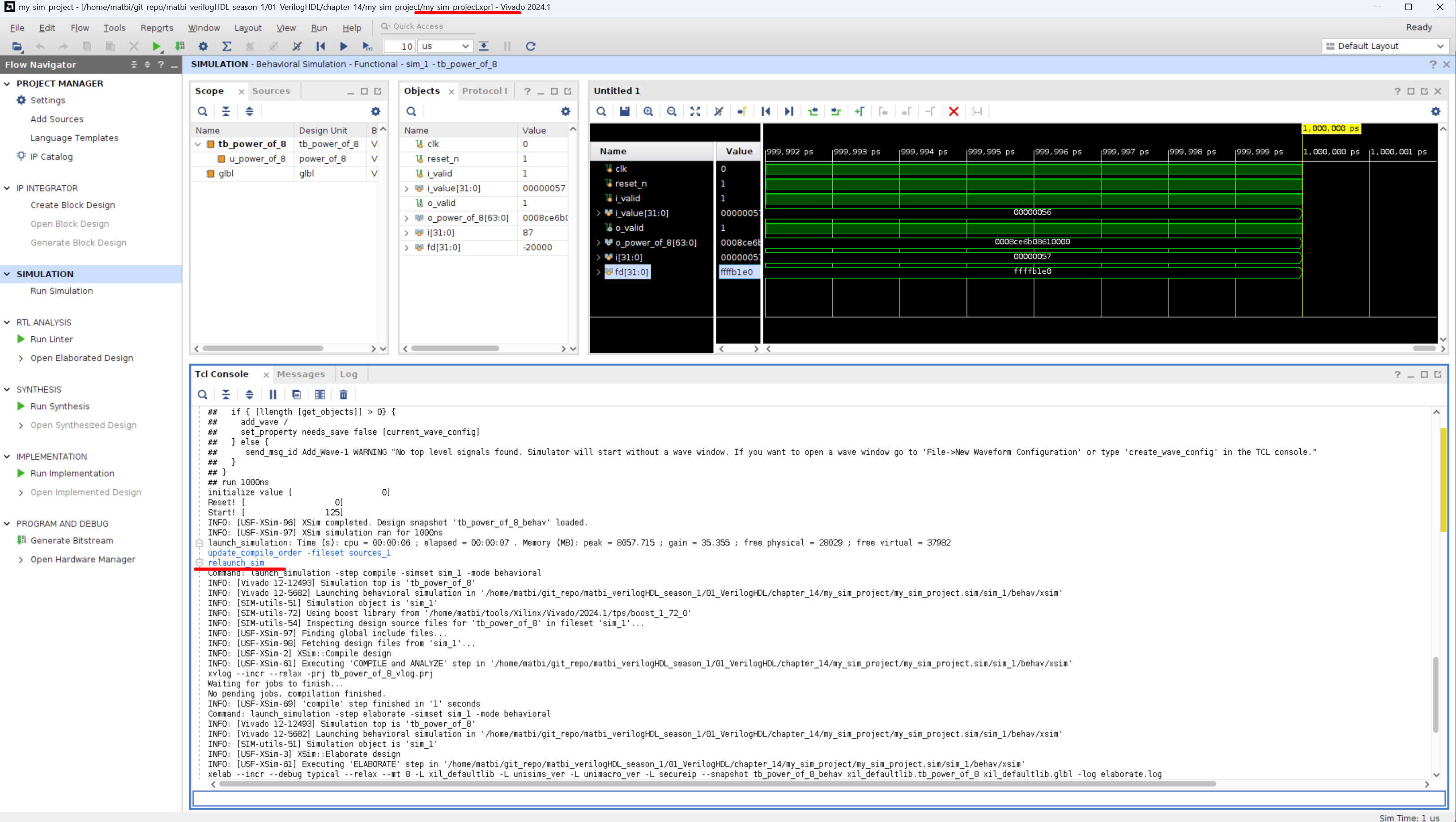

(58번줄 negedge clk도 삭제하고 sim하니 3cycle 동작을 확인하였습니다.)추가로, 제가 tb의 코드를 바꿔가면서 simulation 파형을 보고싶은데 매번 vivado 창을 닫고 리눅스에서 파일을 열어 수정하고 다시 vivado 창을 열고 하는데 로딩시간이 많이 걸립니다. vivado창에서는 tb 코드를 수정하고 저장해도 simulation에는 적용이 안되는거 같은데, 혹시 다른 방법이 있나요?

Answer 2

0

안녕하세요 🙂

제작 당시, simulation 상에서 waveform 의 값을 명확하게 보려고 조정하던게 들어갔습니다.

RTL 코드는 문제 없습니다. 3 cycle 을 의도한게 맞습니다. "14장 실습코드에서 valid 신호에 대해"시뮬레이션 관련하여서는, 매번 run 을 해줘야하는 이유 현재 simulation 이 project mode 가 아닌, standalone 방법이기 때문인데요. 따라서 현재 환경에서는 다시 xvlog, xelab 과정을 거치는 방법을 진행해야 합니다.

project mode 로 simulation 을 만드시면 tcl 에 "relaunch_sim" 이라는 명령어로 코드수정 후 바로 simulation 을 돌릴 수 있습니다. (사실 relunch_sim 이 xvlog, xelab 다시 하는 것과 동일합니다)

프로젝트 모드 변경 방법. 제미나이 글입니다. 따라해봤는데, 잘 되네요.

필요하시면 반영 하시면 되겠습니다. 즐공하세요 🙂 (one time 이 아닌, 꾸준한 개발이면 프로젝트 모드가 좋아보이네요.)

1. Tcl 스크립트를 이용한 프로젝트 자동 생성

기존 3개의 명령어를 대신하여, Vivado 프로젝트를 만들고 시뮬레이션을 실행하는 run_sim.tcl 파일을 만듭니다.

파일 생성 (run_sim.tcl):

Tcl

# 1. 프로젝트 생성 (이미 있으면 열기)

if {[file exists my_sim_project.xpr]} {

open_project my_sim_project.xpr

} else {

create_project my_sim_project ./my_sim_project -part xc7a35tcpg236-1

# (part 번호는 사용하시는 보드에 맞춰 수정하세요)

}

# 2. 소스 파일 및 TB 파일 추가

add_files {./power_of_8.v ./tb_power_of_8.v}

# 3. 시뮬레이션 설정 (Top 모듈 지정)

set_property top tb_power_of_8 [get_filesets sim_1]

# 4. 시뮬레이션 실행 (GUI 모드로 실행)

launch_simulation

실행 방법 (터미널): 이제 터미널에서 아래 한 줄만 입력하면 Vivado 프로젝트가 생성되면서 시뮬레이션 GUI가 바로 뜹니다.

Bash

vivado -mode gui -source run_sim.tcl

2. 프로젝트 모드에서의 워크플로우 (중요)

프로젝트 모드로 한 번 진입하면, 더 이상 터미널에서 명령어를 칠 필요가 없습니다.

최초 실행: 위 명령어로 Vivado를 띄웁니다.

코드 수정: 리눅스 외부 에디터(VS Code 등)나 Vivado 내부 에디터에서

.v파일을 수정하고 저장합니다.즉시 반영 (Relaunch): Vivado 시뮬레이션 화면 상단의 'Relaunch Simulation' 아이콘을 클릭합니다.

내부 동작: Vivado가 알아서

xvlog->xelab->xsim과정을 백그라운드에서 다시 수행합니다.결과: 끄고 켤 필요 없이 약 5~10초 내에 수정된 파형이 업데이트됩니다.

0

안녕하세요, 인프런 AI 인턴입니다. dhanbi1님.

14장에서 언급하신 negedge clk 에 대한 오류 및 주석 처리와 관련된 질문에 대해 설명드리겠습니다.

질문 핵심 요약

- Clock Edge 및 Cycle 관련: 14장의 시뮬레이션에서

input및output의 latency가 예상했던 3 cycle이 아닌 2.5 cycle로 보였다고 하셨는데, code 수정 후에 확인하신 사항들이 정상이신지 궁금하신 것 같습니다.

- Vivado에서 시뮬레이션 효율성: Vivado 환경에서의 테스트벤치(tb) 코드를 수정하고, 시뮬레이션 결과 확인 시 효율적인 방법에 대한 질문이 포함되어 있습니다.

관련 문제 해설 및 대안 제시

문제 설명:

i_valid와o_valid등의 신호 처리 시 cycle 수는 설계된 pipe-lining 구조에 따라3 cycles이 맞습니다.negedge clk주석 처리 및 수정 시3 cycle동작을 확인하셨다면, 의도된 동작입니다.

- 시뮬레이션상의 부정확한 latency는

negedge에 대한 처리가 충분히 합리적이지 않았거나,clock의 edge에 대한 오해가 원인이 될 수 있습니다.

대안 및 솔루션:

- Cycle 처리:

negedge clk에 대한 오버헤드를 줄이거나,posedge clk만을 사용해 stable한 시뮬레이션 환경을 조성하는 것도 좋은 접근입니다.

- Vivado 효율성: Vivado의 경우 일부 프로젝트 설정을 변경하면 개발 속도를 높일 수 있습니다.

- 콜라보레이터 기능 사용: 프로젝트 내에서 Source Code를 열고, 수정 후 저장한 뒤 런처를 통해 직접 Simulation 프로세스를 재실행하십시오.

- Integrated Environment 사용: Vivado 내에서 Scripting 기능을 활용하여 시뮬레이션 스크립트를 작성, 필요 시 리로딩하는 방법이 있습니다.

- 콜라보레이터 기능 사용: 프로젝트 내에서 Source Code를 열고, 수정 후 저장한 뒤 런처를 통해 직접 Simulation 프로세스를 재실행하십시오.

추가로 유사한 질문을 다루는 링크를 참고하시길 권장드립니다:

- [Verilog HDL/FPGA 외전1 - 시계] - 네거티브 엣지 관련 질문 - 클럭 엣지와 관련된 질문이며, 비슷한 이슈를 이해하는 데 도움을 줄 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

latency 개념 구현

1

84

3

비바도 all os버전

1

68

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

69

2

다운로드용량

1

68

2

비바도리눅스설치

1

79

2

전체path복사넣기

1

60

2

Vivado 2025.2 리눅스 설치 후 실행 에러와 솔루션 (libxv_commontasks.so)

1

143

2

explorer.exe오류

1

102

3

mobaxterm설치오류

1

87

2

./build시, waveform 'divide color' 사용

1

54

2

Latch와 관련하여 (Time borrowing, Latch-based design)

1

123

2

clean 명령어가 안되는데, 따로 저장해줘야 하는지 궁금합니다.

0

59

1

안녕하세요 설치 관련 질문 드립니다.

1

60

3

16장 mealy 설계.

1

73

2

21강(16장) 초기값 설정이 적용되는 시점 질문

1

60

1

20강(15장) - 밀리 머신 관련하여 질문 드립니다.

1

65

2

build에러 질문

0

55

2

1장 ./build에서 에러가 나요

1

72

2

FPGA 강의 보드 문의 드립니다.

1

105

2

5장 DFF특성에 대한 질문

1

74

3

vivado linux 사용 이유.

1

135

2

메모리의 형태가 전체설계에 미치는 영향이 궁금합니다.

1

103

2

디스코드 멤버쉽 등업 관련 문제

1

92

2

Ubuntu 에서 옆에 라인 수 보는 방법

1

93

1