설계독학맛비's 실전 AI HW 설계를 위한 바이블, CNN 연산 완전정복 (Verilog HDL + FPGA 를 이용한 가속기 실습)

맛비와 함께 AI 하드웨어의 기본을 공부합니다. 비메모리 설계 전문가로서 좋은 AI HW를 설계하기 위한 필수 지식을 담았습니다.

당신의 설계 실력을 점검 받을 시간입니다.

설계독학 Verilog Master Season1 강의가 100% 완성 되었습니다.

실습코드는 다시 한번 받아주시면 감사하겠습니다. (파일명 : SGDH_Verilog_Master_S1_Lecture_100%.zip)

AI 발전으로 인하여 취업이 어렵다고 하지만, 그 모든 기본은 본인의 실력입니다.

AI 가 하지 못하는, 할 수 없는 지식을 쌓고 노하우를 만들면 됩니다.

학사출신 국비강의를 거쳐 -> 중소기업 -> 대기업 -> 외국계 기업까지 입사한 에타님의 노하우를 함께 공부하고, 슬기로운 설계생활 함께해요.

감사합니다.

설계독학 맛비 드림.

안녕하세요. 설계독학의 맛비입니다.

드디어 많은 분들이 기다려주신

📘Verilog 마스터 Season 1강의가 오픈되었습니다!이 강의는 단순한 문법 설명이 아닌,

실제 면접과 코딩 테스트에서 출제된 문제들을 직접 풀어보며

디지털 설계 실력을 스스로 점검하고 실무 감각까지 익힐 수 있는 실전 중심 강의입니다.🧩이 강의는 이런 분들께 추천드립니다.

회로설계 코딩 테스트를 준비 중인 전공자 / 취업 준비생

RTL 설계를 실습 위주로 익히고 싶은 대학원생

Verilog를 실무 수준으로 정리하고 싶은 엔지니어

Testbench까지 구현해보고 싶은 SystemVerilog 입문자

🧠강의 특징 요약

Verilog 실전 설계 문제 40여 개 수록

면접 기출 기반, 실무 활용 가능한 문제 구성

문제 소개 → 풀이 시간 → 해설 → Waveform → Schematic 검토

ETA 님과 맛비가 직접 제작, 검수, 편집한 콘텐츠

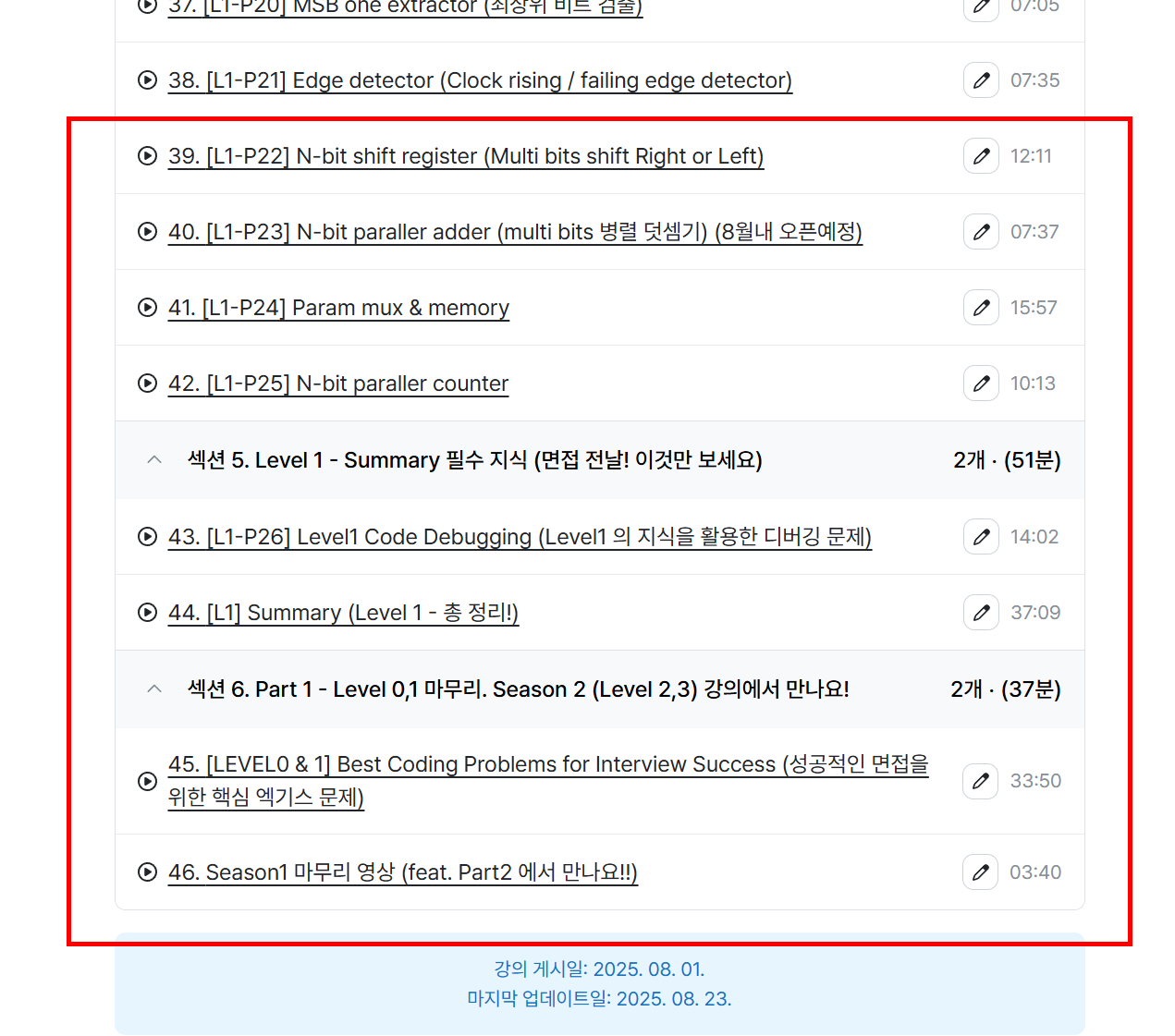

🗂구성 안내

Level 0: 게이트, 카르노맵, FSM 등 기초 개념 문제

Level 1: ALU, 인터럽트, 파이프라인 등 실전 면접 대비 문제

앞으로도 문제는 지속적으로 업데이트 예정입니다.

지금이 가장 문제 수가 적고, 가장 저렴하게 수강하실 수 있는 시점입니다.

수강하신 이후에는 무제한 수강 및 질의응답으로 운영됩니다.이제 여러분의 Verilog 실력을

직접 확인하고 증명하실 차례입니다.Verilog는 선택이 아닌 필수입니다.

Season1으로 기초와 실전을 모두 다지시고,

다가올 Season2(Level 2~3) 에서도 함께 성장해 나가요.강의에서 뵙겠습니다.

감사합니다.

— ETA & 맛비 드림안녕하세요. 설계가족 여러분!

Verilog HDL S2 의 수강 기한이 "기존 1년"에서 "무제한"으로 변경되었습니다. (기존의 B2B 결제는 정책상 제외)

저를 믿고 수강해주셔서 진심으로 감사드리고요.

제가 언제 리타이어가 될지 모르겠지만... ㅠㅠ (나름 젊습니다)

그전까지는 무제한 수강, 질의 응답을 할 수 있도록 최선을 다하겠습니다.

감사합니다!! 생유!!