인프런 커뮤니티 질문&답변

DDR, FIXED I/O 질문드립니다.

작성

·

1.1K

2

안녕하세요 맛비님!!

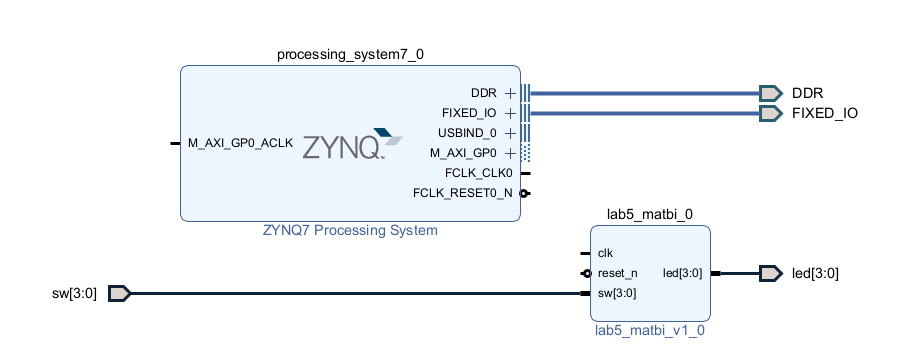

1. 다음 사진처럼, DDR, FIXED I/O, LED가 칩 외부의 보드 핀과 연결되는 것으로 알고 있는데, LED는 출력부분이니까 이해했습니다.

그런데 DDR은 Double Data Rate로, 클럭의 양쪽 엣지를 동기화하여 입력값을 받는다고 알고 있는데 쓰이는 이유가 궁금합니다.

그리고 FIXED I/O는 인터넷에서 찾아보니, Standard I/O 와 연관이 되어있고, Standard I/O 는 LVDS, LVCMOS 등등의 표준 규격으로 알고 있지만, FIXED I/O의 정확한 개념을 잘 모르겠습니다.

(고정된 input output인가요?)

2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁금합니다!

3. create clock으로 주기를 만들어줄 수 있는것으로 알고있는데, xdc파일 클럭 관련 문법을 안쓰고 zynq ip로 clock부분 활성화 시키는지 궁금합니다!

- 강의 내용외의 개인 질문은 받지 않아요 (개별 과제, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

답변 1

1

설계독학맛비

지식공유자

안녕하세요 :)

1. 다음 사진처럼, DDR, FIXED I/O, LED가 칩 외부의 보드 핀과 연결되는 것으로 알고 있는데, LED는 출력부분이니까 이해했습니다.

그런데 DDR은 Double Data Rate로, 클럭의 양쪽 엣지를 동기화하여 입력값을 받는다고 알고 있는데 쓰이는 이유가 궁금합니다.

"DDR 에서 Double data rate 를 사용하는이유" 라고 해석이 되는데, 이 부분은 BW 를 두배로 늘리기 위함입니다. 자세한건 구글링 부탁드립니다.

그리고 FIXED I/O는 인터넷에서 찾아보니, Standard I/O 와 연관이 되어있고, Standard I/O 는 LVDS, LVCMOS 등등의 표준 규격으로 알고 있지만, FIXED I/O의 정확한 개념을 잘 모르겠습니다.

(고정된 input output인가요?)

말그대로 고정된 I/O 입니다.

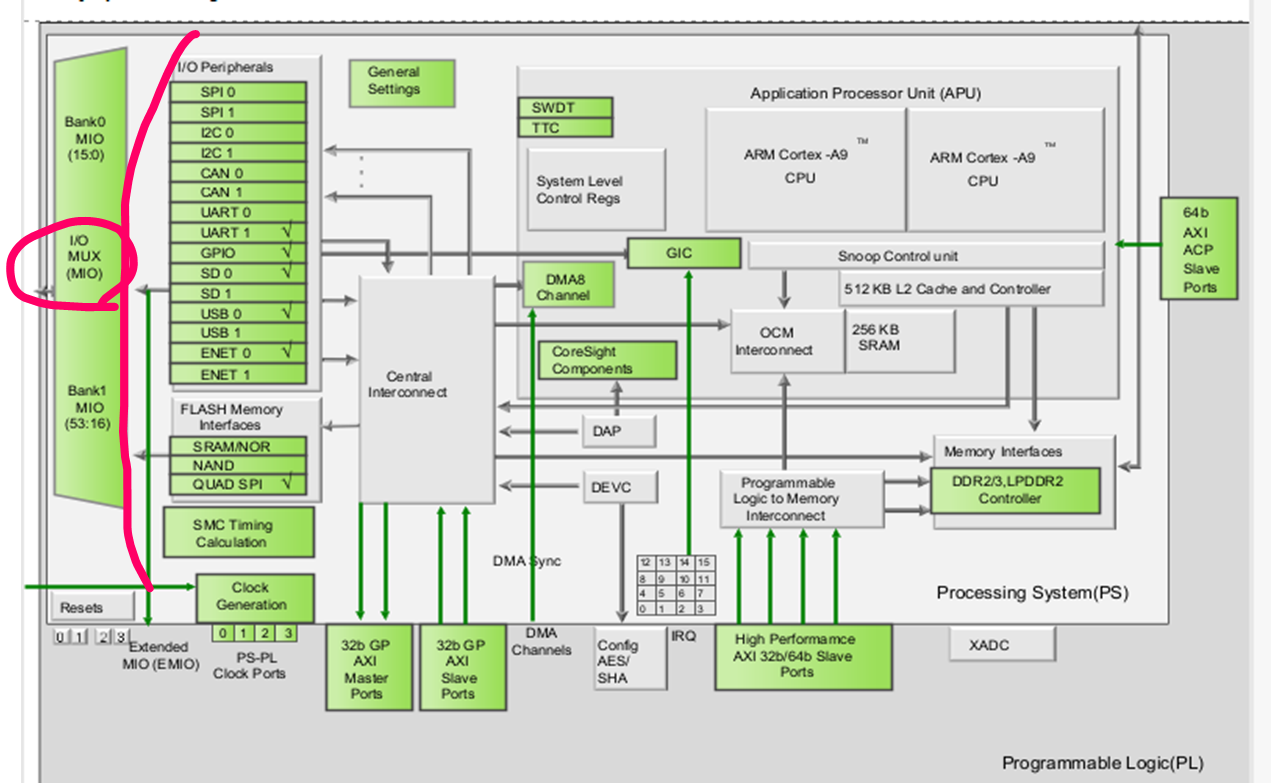

다음 그림처럼 펼쳐서 보면 MIO 가 있습니다.

이 MIO 는 다음 그림을 참고하세요.

2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁금합니다!

강의의 내용을 더 진행하시다 보면, Vitis 사용합니다. :)

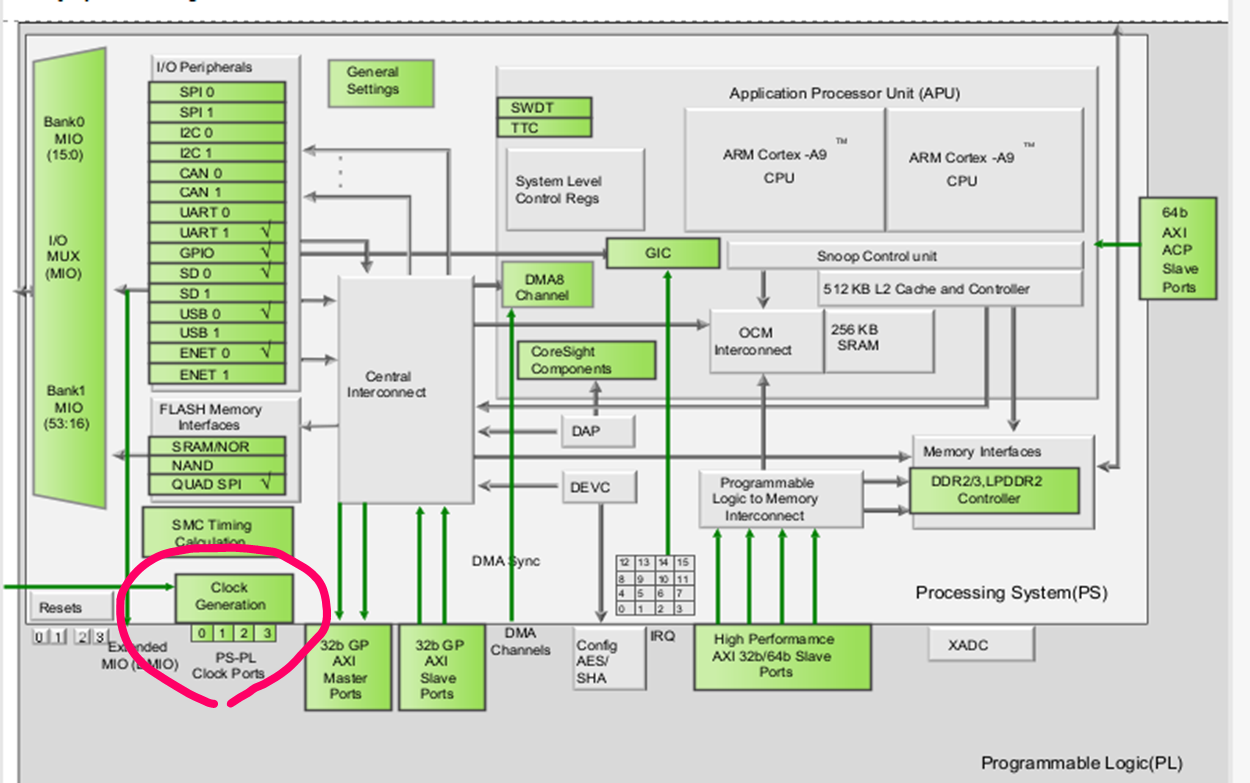

3. create clock으로 주기를 만들어줄 수 있는것으로 알고있는데, xdc파일 클럭 관련 문법을 안쓰고 zynq ip로 clock부분 활성화 시키는지 궁금합니다!

zynq 의 ARM 에서 만들어주는 Clock 을 사용함으로, xdc file 을 통해 명시하지 않아도 됩니다.

외부 오실레이터의 clock 을 입력받아서 사용한다면 알고계신 xdc 파일 클럭 문법을 사용하시면 됩니다.

즐공하세요 :)

맛비님 답변 정말 감사합니다!

2번 질문을 제가 잘못했습니다!

2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁금합니다!

-> Vivado에서 바로 open hardware 후 program device를 해서 FPGA에 올리지 않고, Vitis를 사용하여, FPGA에 올리는 이유가 궁금합니다!

로 정정하겠습니다

감사합니다 :)