인프런 커뮤니티 질문&답변

HW Run 부분 pipeline 질문

해결된 질문

작성

·

431

4

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

먼저 연휴 전에 질문을 드리게 되어 죄송합니다 TT

이번 실습 HW RUN 부분은 BRAM에 Write, Core Run, BRAM에 Read 이렇게 3가지 과정으로 나누어서 이루어졌는데, 여기서 Pipeline 개념 관련해서 질문이 있습니다.

1. HW RUN 과정에서 이미 Pipeline이 적용 되었다고 할 수 있나요?

2. 3가지 과정을 따로 나누지 않고 Pipeline을 적용할 수 있지만, run time 측정을 위해서 일부러 하지 않은 건가요?

Pipeline 개념이 아직 미숙하기도 하고, 이번 실습의 경우에 적용이 가능한지, 적용을 했을 때 오히려 더 느려지게 될 수도 있는건지 감이 안잡히네요 :(

항상 친절한 답변 감사드려요. 즐거운 연휴 되세요!

항상 친절한 답변 감사드려요. 즐거운 연휴 되세요!

퀴즈

FPGA 기반 하드웨어 가속기 설계에서 Data Mover BRAM 모듈의 주된 역할은 무엇일까요?

CPU가 복잡한 알고리즘을 효율적으로 실행하도록 돕습니다.

FPGA 내부의 두 BRAM 메모리 간에 데이터를 효과적으로 전송합니다.

소프트웨어 코드를 하드웨어 명령으로 변환하는 역할을 합니다.

FPGA 칩의 전력 소모량을 줄여줍니다.

답변 1

1

설계독학맛비

지식공유자

안녕하세요 :)

먼저 새해 복 많이 받으세요.

이번 실습 HW RUN 부분은 BRAM에 Write, Core Run, BRAM에 Read 이렇게 3가지 과정으로 나누어서 이루어졌는데, 여기서 Pipeline 개념 관련해서 질문이 있습니다.

1. HW RUN 과정에서 이미 Pipeline이 적용 되었다고 할 수 있나요?

답이 좀.. 어렵습니다. 3년차 이상의 설계지식이 필요하다 생각합니다.

이해가 안되셔도 너그럽게 넘어가주세요. 직접 해보셔야 알 수 있습니다.

최대한 성심성의껏 쉽게 적어보겠습니다.

BRAM에 Write, Core Run, BRAM에 Read 관점에서 보았을때, Pipeline 이 미적용되어 있습니다.

Verilog HDL 시간에서 배우셨겠지만, Pipeline 을 유지하려면, 저장공간 이 필요합니다.

현재 구조에서는 BRAM 의 Double 사용이 필요합니다. 즉, 쉬지 않고 동작하기 위한 Buffer 가 필요합니다.

다만 pipeline 을 유지한다고해도 Performance 향상이 되겠지만, 현재는 AXI4-Lite 로 Write / Read 를 하고 있기때문에, 이 부분을 개선하는것이 Performance 향상에 큰 도움이 되실 겁니다.

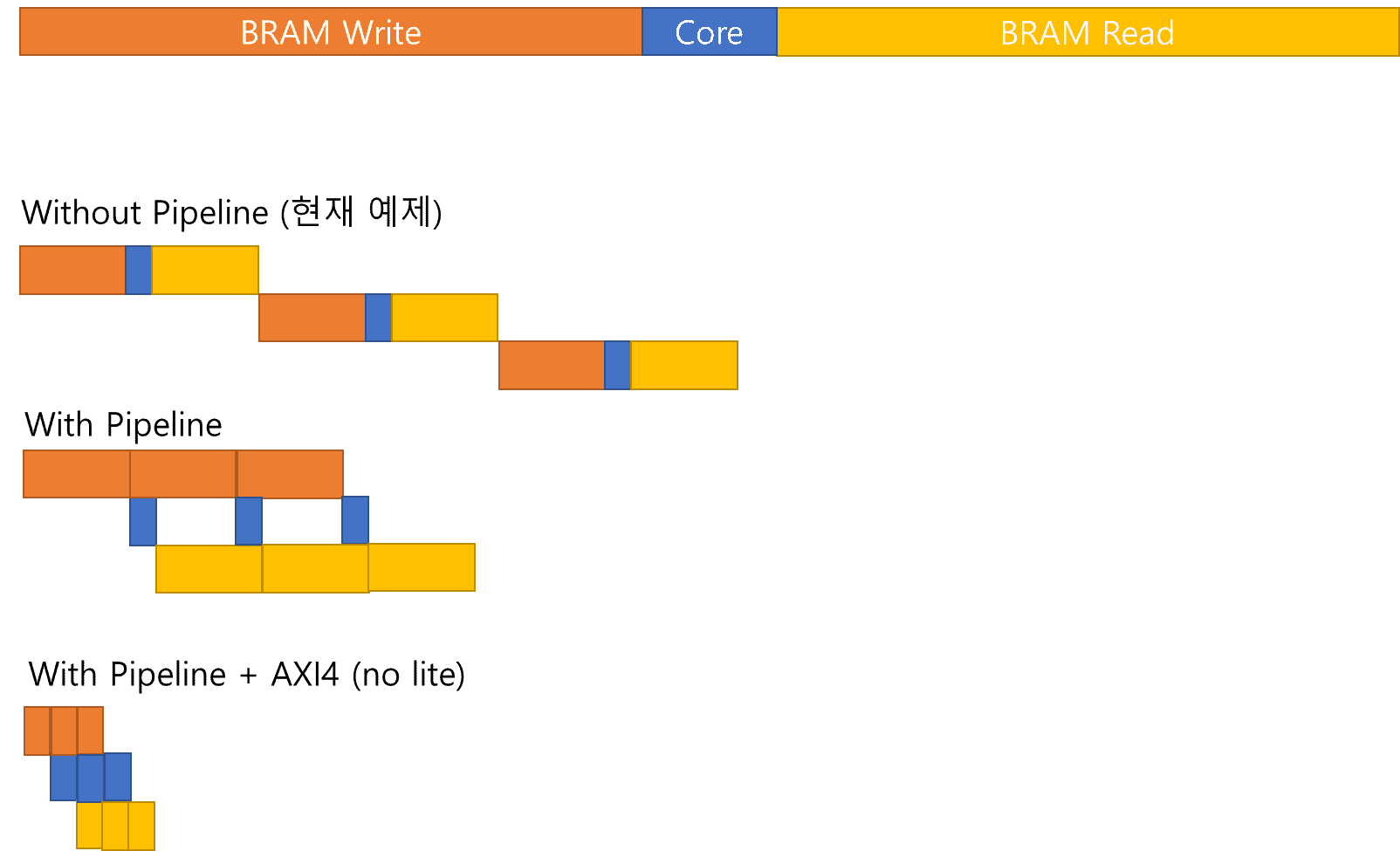

막대기의 길이가 running time 이다 했을때의 그림입니다.

AXI4 의 DMA 를 설계하실 줄 알면 되구요. 이 부분은 Verilog HDL season 2 에서 마지막 Project 로 계획중입니다. 올해 중순에 시작해서 올해 말 혹은 내년 초 완료로 강의를 계획중입니다.

맨 마지막 그림으로 설계가 되면 됩니다. (실제 가속기 제품의 이상적인 시나리오입니다.)

Pipeline 과 AXI 사용 :)

2. 3가지 과정을 따로 나누지 않고 Pipeline을 적용할 수 있지만, run time 측정을 위해서 일부러 하지 않은 건가요?

구현 난이도 때문에 이 과정에서는 뺏습니다.

현재 구조에서 Pipeline 을 적용하려면 다음 부분이 수정되어야합니다.

BRAM 의 double buffering (ping-pong buffer) 설계가 필요합니다 :)

Pipeline 개념이 아직 미숙하기도 하고, 이번 실습의 경우에 적용이 가능한지, 적용을 했을 때 오히려 더 느려지게 될 수도 있는건지 감이 안잡히네요 :(

Pipeline 은 최대한! 적용할 수 있으면 해야합니다.

HW 설계의 미덕입니다.

즐공하세요 :)

답변을 이해하는데 그림이 큰 도움을 주네요 :D

덕분에 궁금한 점들 해결되었습니다!

항상 감사드립니다.