인프런 커뮤니티 질문&답변

SW에서 필요한 메모리

작성

·

229

1

안녕하세요,

1. 수업 [FPGA 19장] 10:50 경

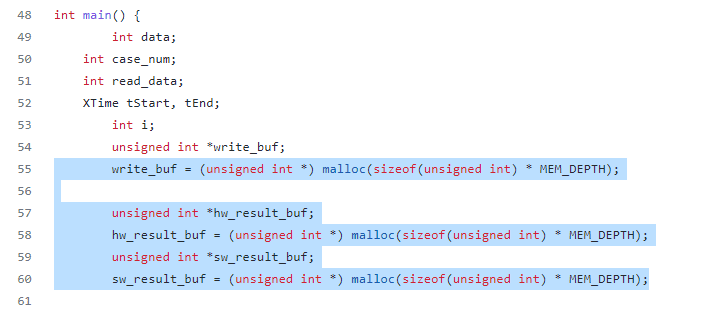

4byte*4096*2ea = 32768byte + (추가 malloc 16384 byte) 이라는 자막이 등장하는데, 32768byte는 어디서 기인하는지 이해를 하였는데, 여기서 (추가 malloc 16384 byte)는 어디서 갑자기 생긴 건지 별다른 설명이 없어서 이 부분이 궁금합니다.

2. 또한 lscript에서 stack size와 head size를 더 크게 변경해주는데 이때 다루는 메모리 영역은 PS 영역인가요? PL 영역인가요? (arm 칩이겠죠...?)

3. 또한 lscript에서 stack size와 head size를 더 크게 변경해주는데 그 limit, 혹은 한도가 존재할텐데 그 제한점은 어디서 확인할 수 있으며, 만약 그 메모리가 부족하다면, 더 추가할 수 있는지 궁금합니다.

감사합니다.

퀴즈

FPGA 기반 하드웨어 가속기 설계에서 Data Mover BRAM 모듈의 주된 역할은 무엇일까요?

CPU가 복잡한 알고리즘을 효율적으로 실행하도록 돕습니다.

FPGA 내부의 두 BRAM 메모리 간에 데이터를 효과적으로 전송합니다.

소프트웨어 코드를 하드웨어 명령으로 변환하는 역할을 합니다.

FPGA 칩의 전력 소모량을 줄여줍니다.

답변 1

0

설계독학맛비

지식공유자

안녕하세요 :)

1. 수업 [FPGA 19장] 10:50 경

4byte*4096*2ea = 32768byte + (추가 malloc 16384 byte) 이라는 자막이 등장하는데, 32768byte는 어디서 기인하는지 이해를 하였는데, 여기서 (추가 malloc 16384 byte)는 어디서 갑자기 생긴 건지 별다른 설명이 없어서 이 부분이 궁금합니다.

malloc 이 총 3개가 되어 있구요.

- hw+sw (32768)

- write_buf (16384)

이렇게 이해해주시면 될 것 같아요.

2. 또한 lscript에서 stack size와 head size를 더 크게 변경해주는데 이때 다루는 메모리 영역은 PS 영역인가요? PL 영역인가요? (arm 칩이겠죠...?)

Yes (PS)

3. 또한 lscript에서 stack size와 head size를 더 크게 변경해주는데 그 limit, 혹은 한도가 존재할텐데 그 제한점은 어디서 확인할 수 있으며, 만약 그 메모리가 부족하다면, 더 추가할 수 있는지 궁금합니다.

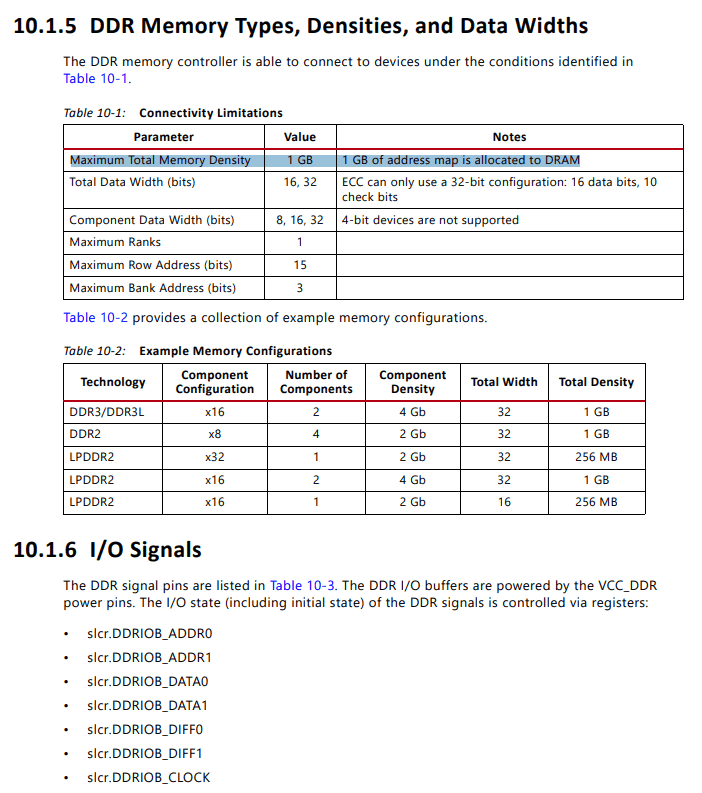

해당 부분은 저도 자세히는 모르지만, 문서를 찾아보니까. (firmware 엔지니어 분이 잘 아실 것 같긴하네요)

PS 가 접근 가능한 최대 메모리는 크기는 1GB 일 것 같아요.

정답은 아닙니다 ㅎ 그럴 것 같다? 수준의 확신이에요.

즐공하세요 :)