인프런 커뮤니티 질문&답변

reset_n 관련 질문

작성

·

507

1

안녕하세요,

수업을 여러번 복기 하는 중, 의문점이 생겨 질문드립니다.

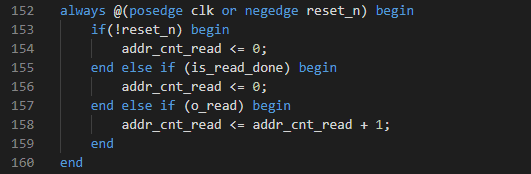

data_mover_bram.v 코드 중, 사진으로 첨부한 부분을 보면

만약 reset_n이 주어지지 않고 바로 data_mover가 동작하게 된다면, addr_cnt_read가 initialize가 되지 않은 상태에서 increment 동작 (addr_cnt_read <= addr_cnt_read +1)을 하게 됩니다.

따라서 코드 진행 중에 문제를 발생시킬 것 같은데, 제 생각이 맞나요? (쓰레기 값 + 1 이 되겠죠...?)

추가적으로 lab22_main.c에서 HW에게 resent_n을 주는 코드를 찾지 못하였는데, 그럼에도 잘 작동하는 이유가 무엇일까요?

감사합니다.

퀴즈

Fully Connected Layer의 핵심 연산은 무엇일까요?

컨볼루션

풀링

입력과 가중치의 곱 합산

활성화 함수 적용만