인프런 커뮤니티 질문&답변

코드 리뷰 중 질문드립니다.

작성

·

308

1

안녕하세요,

FC core 구현 과정 중 data_mover_bram 코드에서 질문드립니다.

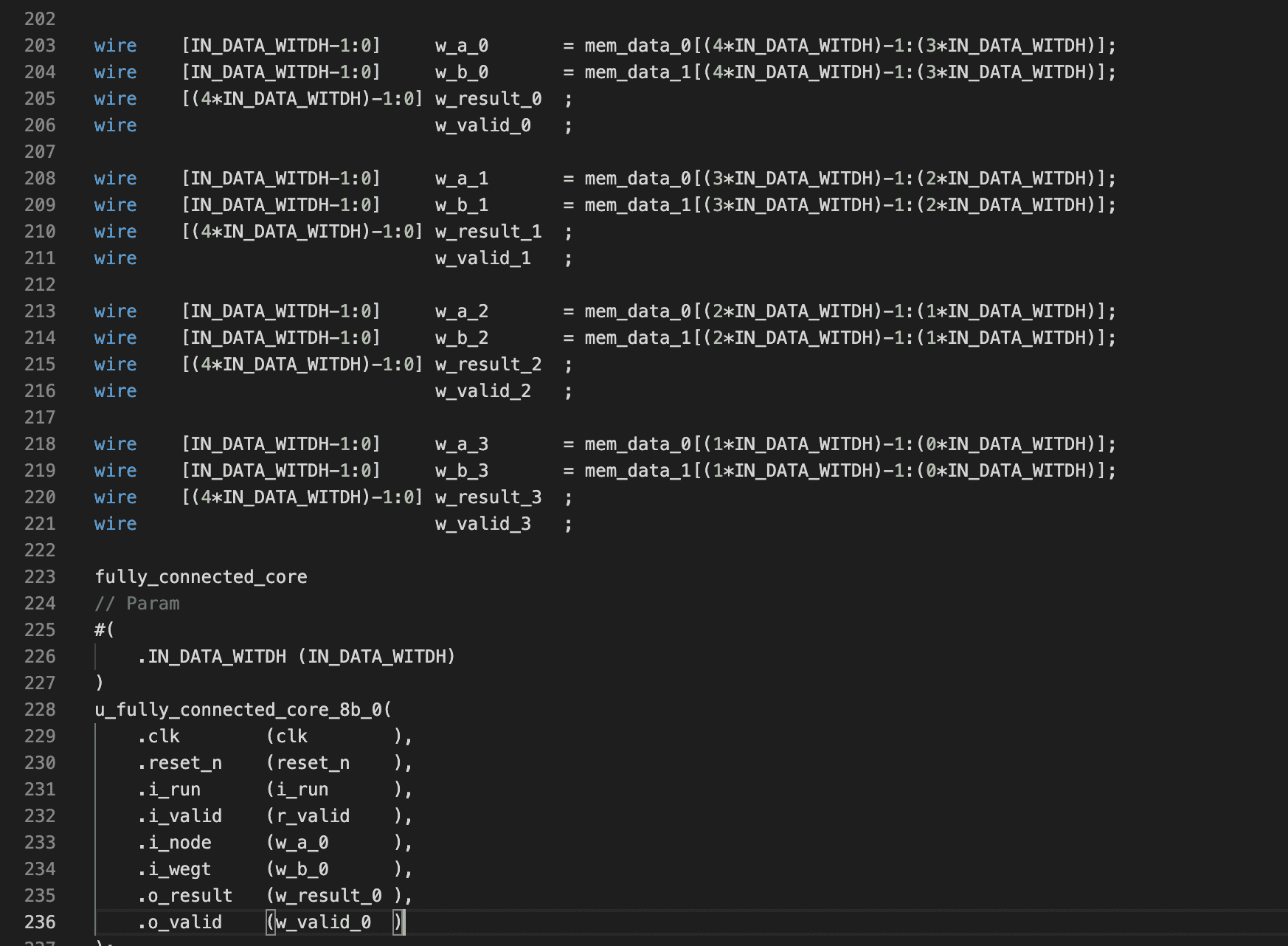

line 203~206 / line 208~211 / line 213~216 / line 218~221은 일정한 규칙을 가지고 비슷한 형태를 가지는 코드입니다.

또한 line 223~237 도 비슷한 형식으로 4개가 있을 것입니다.

궁금한 점은 다음과 같습니다.

1. 현재는 4개의 core를 사용하기 때문에 일일히 코드 작성이 부담이 되지 않지만 실제 fc layer는 엄청 많은 node들로 이루어져 있기 때문에 일일히 일정한 규칙에 맞춰서 매 line을 적어주는 일은 비효율적이라고 생각이 드는데 혹시 이 상황에서 쓸 수 있는 문법이 있는지

2. 비슷하게 module instatiation도 동일하게 비슷한 모듈을 엄청 많이 만들어야한다면 사용 가능한 특정 문법이 있는지

3. 위 두 문법이 이 코드에도 적용될 수 있는지

궁금합니다.

감사합니다.

퀴즈

Fully Connected Layer의 핵심 연산은 무엇일까요?

컨볼루션

풀링

입력과 가중치의 곱 합산

활성화 함수 적용만

안녕하세요 :)

답이 늦었습니다. (연휴라 밖에 있었네요)

generate 문을 쓰면 궁금하신 부분을 해소할 수 있지 않을까 생각합니다.

해당 코드는, AI HW 에서 다룰거라서 조금만 기다려주세요.

이렇게 사용이 가능하다, 정도만 봐주시면 좋을 것 같습니다.

다음은 generate 문법 사용 예이구요.

백문이 불여코드라 코드를 드립니다. 즐공하세요 :)