인프런 커뮤니티 질문&답변

PL to PS Interrupt 관련 문의 사항

작성

·

839

1

안녕하세요?

Zynq 공부에 큰 도움이되고 있습니다. 감사합니다.

강의 내용은 아니지만 PL to PS Interrupt 관련해서 질문드립니다.

질문

==========================================================================

블럭 디자인에서 포트를 생성하여 interrupt 설정 후 IRQ_F2P[0:0]에 연결하면 Interrupt가 활성화 됩니다. (실제 실행 확인)

강의에 사용된 IP를 사용하는 경우 Interrupt가 활성화가 않됩니다. 추가 설정해야 하는 부분이 있는건가요?

==========================================================================

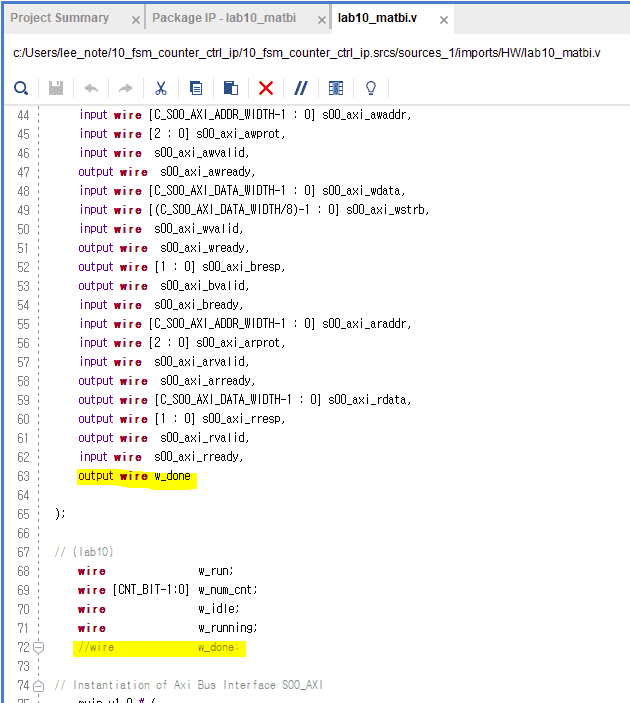

10_fsm_counter 프로젝트의 IP를 사용하여 첨부된 그림1과 같이 수정 하였으며

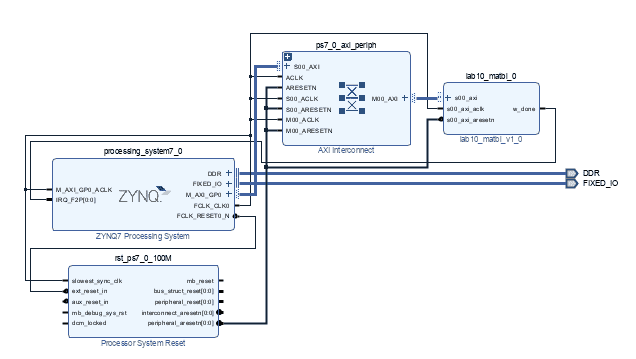

블럭은 첨부된 그림2와 같습니다.

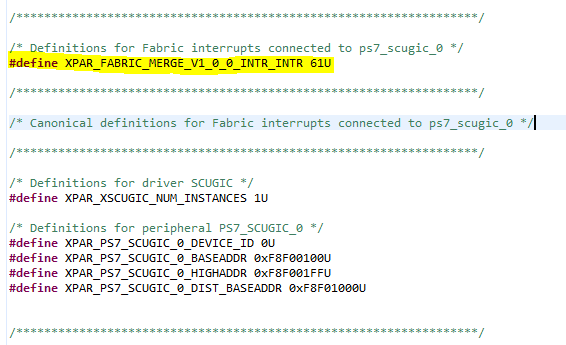

Bitstream 완료 후 Export Hardware로 Inculde bitstream 하여 Vits에서 xparameters.h 를 확인하면 첨부된 그림3과 같은

인터럽트 정의가 없어서 문의 드립니다.

추가 설정해야 하는 부분이 있는것인지 어떤 부분에서 문제가 발생했는지 혹시 알수 있을까요?

감사합니다.

답변 1

0

안녕하세요 :)

(저도 잘 모... 르지만)

제 생각에는 참고한 링크대로만 하면 정상적으로 동작을 할 것 같은데요.

http://www.globaltek.kr/zynq-interrupt-example-tutorial/

하신 방법에는 문제가 있어보이지는 않아요. (irq 체크하고, port 연결만 해주면 될 것 같은데요)

혹시 이거 한번 확인해 보시겠어요?

참고링크의 맨 밑에 보니까, helloworld.c 코드가 있는데, 여기 코드를 vitis 에서 그대로 가져왔을때, compile error 가 있는지 보고 싶어요.

(Vits에서 xparameters.h 에 IRQ 가 없다고 해서, 동작이 안된다, 처럼 보여지지는 않아요.)

XPAR_FABRIC_EXT_IRQ_INTR 이라는 define 이 현재 vitis 프로젝트에서 검색이 되실까요? (search?) 되시면 이걸로 대체해도 될 것 같은..?!

즐공하세요 :)