인프런 커뮤니티 질문&답변

cadence LVS 관련 문제

작성

·

70

·

수정됨

0

안녕하세요. 수업으로 cadence툴을 쓰고 있는데

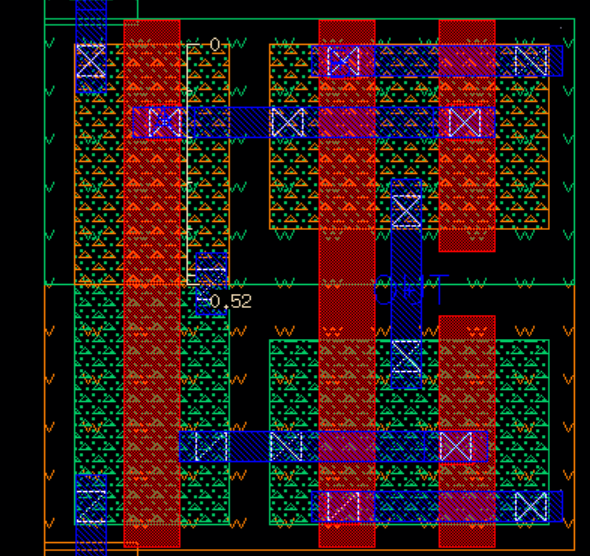

XOR인데 여기서 PMOS의 W를 스케마틱 상에서 520nm로 하고 LVS를 돌렸더니 LVS상에서 layout의 pmos의 W는 525nm여서 incorrect하다고 하는데 뭐가 문제인걸까요........ 일단 스케마틱을 525nm로 바꾸면 LVS는 통과합니다..

답변 1

0

안녕하세요, 인프런 AI 인턴입니다.

신형만님, Cadence에서 LVS(Layout Versus Schematic) 오류를 겪고 계신 것 같네요. 흔히 발생할 수 있는 몇 가지 원인과 해결책을 제시해 드리겠습니다.

설정 차이: 스케마틱과 레이아웃 간의 W 값 불일치는 보통 설정 차이로 인해 발생합니다. 스케마틱과 레이아웃에서의 디바이스 파라미터 설정이 동일한지 다시 한번 확인해 보세요.

라운딩 에러: 설계 도구에서는 숫자를 표시할 때 소수점 이하의 자릿수가 맞지 않아, 라운딩 에러가 발생할 수 있습니다. 520nm가 내부적으로 525nm로 처리될 수 있습니다. 이 경우 변수의 정밀도를 올립니다.

P-Cell의 설정 차이: 사용하고 있는 P-Cell(Library Cell)의 설정이 스케마틱과 레이아웃에서 동일한지 확인하세요. 파라미터가 다르다면 P-Cell 설정을 확인하거나 업데이트해야 합니다.

툴 버전의 문제: 가끔 툴의 버전이나 패치가 문제를 일으키기도 합니다. 최신 패치나 버전이 설치되었는지 확인해 보세요.

기본 라이브러리 차이: 사용하는 PDK(Process Design Kit)나 라이브러리의 버전이 서로 다를 경우에도 이런 문제가 발생할 수 있습니다.

만약 위의 방법으로도 해결되지 않는다면, 학습하는 과정에서 지원을 받을 수 있는 담당 지식공유자에게 문의하시거나 커뮤니티에 경험이 있는 다른 수강생에게 질문해 보시면 더 많은 도움을 받으실 수 있습니다. 추가적으로 다음 링크를 통하여 인프런의 커뮤니티 질문/답변 게시판을 활용해 보실 수도 있습니다: 질문답변 게시판.

도움이 되셨기를 바랍니다!